# **SpringerBriefs in Applied Sciences and Technology** Computational Intelligence

João L. C. P. Domingues · Pedro J. C. D. C. Vaz · António P. L. Gusmão · Nuno C. G. Horta · Nuno C. C. Lourenço · Ricardo M. F. Martins

Speeding-Up Radio-Frequency Integrated Circuit Sizing with Neural Networks

SpringerBriefs in Applied Sciences and Technology

# **Computational Intelligence**

# **Series Editor**

Janusz Kacprzyk, Systems Research Institute, Polish Academy of Sciences, Warsaw, Poland

SpringerBriefs in Computational Intelligence are a series of slim high-quality publications encompassing the entire spectrum of Computational Intelligence. Featuring compact volumes of 50 to 125 pages (approximately 20,000-45,000 words), Briefs are shorter than a conventional book but longer than a journal article. Thus Briefs serve as timely, concise tools for students, researchers, and professionals.

João L. C. P. Domingues · Pedro J. C. D. C. Vaz · António P. L. Gusmão · Nuno C. G. Horta · Nuno C. C. Lourenço · Ricardo M. F. Martins

# Speeding-Up Radio-Frequency Integrated Circuit Sizing with Neural Networks

João L. C. P. Domingues Instituto Superior Técnico Instituto de Telecomunicações Lisbon, Portugal

António P. L. Gusmão Instituto Superior Técnico Instituto de Telecomunicações Lisbon, Portugal

Nuno C. C. Lourenço D Instituto Superior Técnico Instituto de Telecomunicações Lisbon, Portugal Pedro J. C. D. C. Vaz Instituto Superior Técnico Instituto de Telecomunicações Lisbon, Portugal

Nuno C. G. Horta D Instituto Superior Técnico Instituto de Telecomunicações Lisbon, Portugal

Ricardo M. F. Martins Instituto Superior Técnico Instituto de Telecomunicações Lisbon, Portugal

ISSN 2191-530XISSN 2191-5318 (electronic)SpringerBriefs in Applied Sciences and TechnologyISSN 2625-3704ISSN 2625-3712 (electronic)SpringerBriefs in Computational IntelligenceISBN 978-3-031-25098-9ISBN 978-3-031-25099-6 (eBook)https://doi.org/10.1007/978-3-031-25099-6

© The Author(s), under exclusive license to Springer Nature Switzerland AG 2023

This work is subject to copyright. All rights are solely and exclusively licensed by the Publisher, whether the whole or part of the material is concerned, specifically the rights of translation, reprinting, reuse of illustrations, recitation, broadcasting, reproduction on microfilms or in any other physical way, and transmission or information storage and retrieval, electronic adaptation, computer software, or by similar or dissimilar methodology now known or hereafter developed.

The use of general descriptive names, registered names, trademarks, service marks, etc. in this publication does not imply, even in the absence of a specific statement, that such names are exempt from the relevant protective laws and regulations and therefore free for general use.

The publisher, the authors, and the editors are safe to assume that the advice and information in this book are believed to be true and accurate at the date of publication. Neither the publisher nor the authors or the editors give a warranty, expressed or implied, with respect to the material contained herein or for any errors or omissions that may have been made. The publisher remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

This Springer imprint is published by the registered company Springer Nature Switzerland AG The registered company address is: Gewerbestrasse 11, 6330 Cham, Switzerland

# Preface

In the present day, the integrated circuit (IC) industry has, now more than ever, a massive demand for electronic devices not only for the consumer electronics markets but also in other industries such as medical, automotive, or security. Despite Moore's Law not really being observed anymore, the evolution of the IC industry is still clearly observable every year, with designers building increasingly more complex, power-efficient, and integrated systems. These systems often combine analog and digital sections, where most components are integrated into a single chip originating mixed-signal systems-on-a-chip. While these ICs are implemented mainly using digital circuitry, analog operations are still fundamental and irreplaceable. Additionally, technologies such as the Internet of things or fifth-generation broadband join millions of devices and sensors. All these applications continuously gather an increasing amount of data, posing unprecedented challenges to each element of the networks. Due to this, today's market is highly conditioned by the strong demand for high communication rates, large bandwidths, and ultra-low power consumptions, in which radio-frequency (RF) ICs play a critical role. However, analog design is unlike digital design, where an automated flow is established for most design stages. The absence of effective and established computer-aided design tools for electronic design automation of analog and radio-frequency IC blocks poses a significant contribution to their bulky development cycles, leading to long, iterative, and error-prone designer intervention over their entire design flow.

In the past years, automatic simulation-based sizing approaches became essential in designing analog and radio-frequency IC blocks for modern applications to ensure their robustness. However, optimizations considering process, voltage, and temperature (PVT) corners or layout still pose unprecedented challenges in applying these tools due to the high simulation times and different simulator convergence issues. Therefore, the work presented in this book addresses the automatic sizing of analog ICs assisted by deep learning and artificial neural networks on two fronts. First, it proposes two deep learning models to assist the PVT-inclusive simulation-based sizing process of radio-frequency ICs, specifically, voltage-controlled oscillators (VCOs). Given specific devices' dimensions, the first model classifies the likelihood of the circuit to convergence for nominal and PVT corner cases, bypassing solutions that will hardly produce valuable information for the optimization process. The model also predicts the VCOs' oscillating frequencies for the mentioned conditions. The methodology is tested on a state-of-the-art VCO, reducing 19% of the workload of the circuit simulator, ultimately saving almost 5 days of computational effort and improving the optimization result. Secondly, a PVT regressor is proposed, which inputs the circuit's sizing and the nominal performances to estimate the PVT corner performances via multiple parallel artificial neural networks. Two control phases prevent the optimization process from being misled by inaccurate performance estimates. The proposed controlled PVT estimator is tested on two state-of-the-art VCOs, reducing the workload of the circuit simulator up to 79% while achieving a speed-up factor of  $2.92 \times$ , ultimately saving more than 16 days of computational effort. Both methodologies can be used simultaneously, and ultimately, they offer a unique opportunity to reuse valuable legacy data, often discarded in optimization environments.

Finally, the authors would like to express gratitude for the financial support that made this work possible. The work developed in this book was supported by FCT/MCTES through national funds and when applicable co-funded EU funds under the project UIDB/50008/2020 (including internal research project LAY(RF)<sup>2</sup>/X-0002-LX-20) and Research Grant FCT-SFRH/BD/07123/2021.

This book is organized into four chapters.

Chapter 1 presents an introduction to the analog IC design area and discusses how the advances in machine learning can pave the way for new EDA tools.

Chapter 2 presents a study of the available tools for analog design automation. Starting with an overview of existing works where machine learning techniques are applied to analog IC sizing.

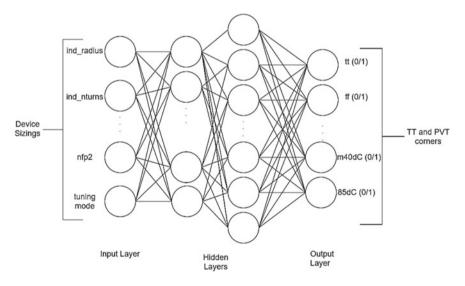

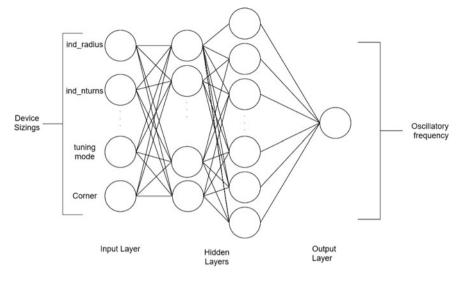

Chapter 3 presents two artificial neural network models for analog IC design to be incorporated within simulation-based sizing loops. The first model classifies the convergence of the circuit for nominal and PVT corners, bypassing solutions that will hardly produce valuable information for the evolutionary kernel, and the second predicts the pre-defined simulator values for the previous conditions.

Chapter 4 presents a controlled PVT regressor based on an artificial neural network, also intended to be incorporated within simulation-based synthesis. This regressor estimates the complete set of PVT corner performances via multiple parallel networks.

Lisbon, Portugal

João L. C. P. Domingues Pedro J. C. D. C. Vaz António P. L. Gusmão Nuno C. G. Horta Nuno C. C. Lourenço Ricardo M. F. Martins

# Contents

| 1 | Intr | oduction                                                | 1  |

|---|------|---------------------------------------------------------|----|

|   | 1.1  | Analog/RF Integrated Circuit Design Automation          | 1  |

|   | 1.2  | Analog IC Design Flow                                   | 3  |

|   | 1.3  | Machine Learning and Analog IC Sizing                   | 4  |

|   | 1.4  | Conclusion                                              | 6  |

|   | Refe | erences                                                 | 6  |

| 2 | Bac  | kground and Related Work                                | 9  |

|   | 2.1  | Knowledge-Based Sizing                                  | 9  |

|   | 2.2  | Optimization-Based Sizing                               | 9  |

|   |      | 2.2.1 Equation-Based Evaluation                         | 9  |

|   |      |                                                         | 10 |

|   | 2.3  | Machine Learning in Simulation-Based Evaluation         | 12 |

|   |      | 2.3.1 Types of Supervision                              | 13 |

|   |      |                                                         | 14 |

|   |      | 2.3.3 Simulation-Based Sizing Enhanced with ANNs        | 15 |

|   | 2.4  | Other ML/DL Efforts on Analog/RF Sizing                 | 18 |

|   |      | 2.4.1 Predicting Sizing from Performances               | 18 |

|   |      | 2.4.2 Reinforcement Learning                            | 19 |

|   | 2.5  | Case Study                                              | 20 |

|   |      | 2.5.1 Dual-Mode Class C/D VCO                           | 20 |

|   |      | 2.5.2 Dataset Generation                                | 22 |

|   | 2.6  | Conclusion                                              | 24 |

|   | Refe | erences                                                 | 24 |

| 3 | Con  | vergence Classifier and Frequency Guess Predictor Based |    |

|   |      |                                                         | 29 |

|   | 3.1  | Contributions                                           | 29 |

|   | 3.2  |                                                         | 30 |

|   |      |                                                         | 30 |

|   | 3.3  |                                                         | 32 |

|   |      |                                                         | 32 |

|   |                                         | 3.3.2                                                                                                                                      | Feature Engineering                                | 35                                                                           |

|---|-----------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|------------------------------------------------------------------------------|

|   |                                         | 3.3.3                                                                                                                                      | Convergence Classifier and Its Hyperparameters     | 35                                                                           |

|   |                                         | 3.3.4                                                                                                                                      | Regressor and Its Hyperparameters                  | 39                                                                           |

|   |                                         | 3.3.5                                                                                                                                      | Final Model Details                                | 42                                                                           |

|   |                                         | 3.3.6                                                                                                                                      | Discussion                                         | 44                                                                           |

|   | 3.4                                     | In-the-                                                                                                                                    | -Loop Integration                                  | 45                                                                           |

|   |                                         | 3.4.1                                                                                                                                      | Class C/D VCO for 3.5-to-4.8 GHz @ 50% Threshold   | 48                                                                           |

|   |                                         | 3.4.2                                                                                                                                      | Class C/D VCO for 3.5-to-4.8 GHz @ 75% Threshold   | 53                                                                           |

|   |                                         | 3.4.3                                                                                                                                      | Class C/D VCO for 3.5-to-4.8 GHz @ 90% and 100%    |                                                                              |

|   |                                         |                                                                                                                                            | Thresholds                                         | 55                                                                           |

|   |                                         | 3.4.4                                                                                                                                      | Analysis of the Points Fed to the Simulator        | 57                                                                           |

|   |                                         | 3.4.5                                                                                                                                      | Plug-and-Play Class C/D VCO 2.3 GHz-to-2.5 GHz     | 59                                                                           |

|   |                                         | 3.4.6                                                                                                                                      | Plug-and-Train Ultralow-Power Class B/C VCO        | 61                                                                           |

|   | 3.5                                     | Concl                                                                                                                                      | usions and Future Research Directions              | 61                                                                           |

|   |                                         | 3.5.1                                                                                                                                      | Conclusions                                        | 62                                                                           |

|   |                                         | 3.5.2                                                                                                                                      | Future Work                                        | 63                                                                           |

|   | Refe                                    | erences                                                                                                                                    |                                                    | 64                                                                           |

|   | -                                       |                                                                                                                                            |                                                    |                                                                              |

| 4 | Pro                                     | cess, Vo                                                                                                                                   | oltage and Temperature Corner Performance          |                                                                              |

| 4 |                                         |                                                                                                                                            | Mage and Temperature Corner Performance Using ANNs | 67                                                                           |

| 4 |                                         | mator                                                                                                                                      |                                                    | 67<br>67                                                                     |

| 4 | Esti                                    | mator Contri                                                                                                                               | Using ANNs                                         |                                                                              |

| 4 | <b>Esti</b><br>4.1                      | mator<br>Contri<br>Contro                                                                                                                  | Using ANNs                                         | 67                                                                           |

| 4 | <b>Esti</b><br>4.1<br>4.2               | mator<br>Contri<br>Contro                                                                                                                  | Using ANNs                                         | 67<br>68                                                                     |

| 4 | <b>Esti</b><br>4.1<br>4.2               | mator<br>Contri<br>Contro<br>Traini                                                                                                        | Using ANNs                                         | 67<br>68<br>69<br>69<br>72                                                   |

| 4 | <b>Esti</b><br>4.1<br>4.2               | mator<br>Contri<br>Contro<br>Traini<br>4.3.1                                                                                               | Using ANNs                                         | 67<br>68<br>69<br>69                                                         |

| 4 | <b>Esti</b><br>4.1<br>4.2               | mator Contri<br>Contri<br>Traini<br>4.3.1<br>4.3.2                                                                                         | Using ANNs                                         | 67<br>68<br>69<br>69<br>72                                                   |

| 4 | <b>Esti</b><br>4.1<br>4.2               | mator 1<br>Contri<br>Contro<br>Traini<br>4.3.1<br>4.3.2<br>4.3.3<br>4.3.4<br>4.3.5                                                         | Using ANNs                                         | 67<br>68<br>69<br>69<br>72<br>73                                             |

| 4 | <b>Esti</b><br>4.1<br>4.2               | mator 1<br>Contri<br>Contro<br>Traini:<br>4.3.1<br>4.3.2<br>4.3.3<br>4.3.4<br>4.3.5<br>In-the                                              | Using ANNs                                         | 67<br>68<br>69<br>69<br>72<br>73<br>78<br>80<br>81                           |

| 4 | <b>Esti</b><br>4.1<br>4.2<br>4.3        | mator 1<br>Contri<br>Contro<br>Traini<br>4.3.1<br>4.3.2<br>4.3.3<br>4.3.4<br>4.3.5                                                         | Using ANNs                                         | 67<br>68<br>69<br>69<br>72<br>73<br>78<br>80                                 |

| 4 | <b>Esti</b><br>4.1<br>4.2<br>4.3        | mator 1<br>Contri<br>Contro<br>Traini:<br>4.3.1<br>4.3.2<br>4.3.3<br>4.3.4<br>4.3.5<br>In-the                                              | Using ANNs                                         | 67<br>68<br>69<br>72<br>73<br>78<br>80<br>81<br>86<br>89                     |

| 4 | <b>Esti</b><br>4.1<br>4.2<br>4.3        | mator 1<br>Contri<br>Contro<br>Traini:<br>4.3.1<br>4.3.2<br>4.3.3<br>4.3.4<br>4.3.5<br>In-the<br>4.4.1<br>4.4.2<br>4.4.3                   | Using ANNs                                         | 67<br>68<br>69<br>72<br>73<br>78<br>80<br>81<br>86<br>89<br>93               |

| 4 | <b>Esti</b><br>4.1<br>4.2<br>4.3        | mator 1<br>Contri<br>Contro<br>Traini:<br>4.3.1<br>4.3.2<br>4.3.3<br>4.3.4<br>4.3.5<br>In-the<br>4.4.1<br>4.4.2<br>4.4.3                   | Using ANNs                                         | 67<br>68<br>69<br>72<br>73<br>78<br>80<br>81<br>86<br>89<br>93<br>106        |

| 4 | <b>Esti</b><br>4.1<br>4.2<br>4.3        | mator 1<br>Contri<br>Contro<br>Traini:<br>4.3.1<br>4.3.2<br>4.3.3<br>4.3.4<br>4.3.5<br>In-the<br>4.4.1<br>4.4.2<br>4.4.3<br>Conch<br>4.5.1 | Using ANNs                                         | 67<br>68<br>69<br>72<br>73<br>78<br>80<br>81<br>86<br>89<br>93<br>106<br>106 |

| 4 | Esti<br>4.1<br>4.2<br>4.3<br>4.4<br>4.4 | mator 1<br>Contri<br>Contro<br>Traini<br>4.3.1<br>4.3.2<br>4.3.3<br>4.3.4<br>4.3.5<br>In-the<br>4.4.1<br>4.4.2<br>4.4.3<br>Conclu          | Using ANNs                                         | 67<br>68<br>69<br>72<br>73<br>78<br>80<br>81<br>86<br>89<br>93<br>106        |

# Chapter 1 Introduction

# 1.1 Analog/RF Integrated Circuit Design Automation

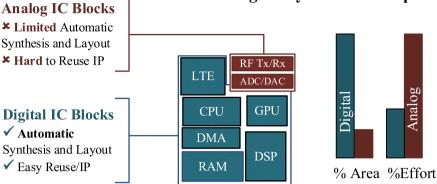

In the present day, the IC industry has, now more than ever, a huge demand for electronic devices not only in the consumer electronics markets but also in other industries such as medical, automotive, or security. Despite Moore's law not really being observed anymore, the evolution of the IC industry is still clearly observable every year, with designers building increasingly more complex, power-efficient and integrated systems. These systems often combine analog and digital sections, where most components are integrated into a single chip originating mixed-signal systemson-a-chip (SoCs). While most functionalities are implemented using digital or digital signal processing circuitry, analog circuits are the bridge between digital circuitry and physical devices with a steady increase in connectivity needs. Even though analog circuits only occupy a small fraction of the SoCs, their design effort is disproportionally large, as illustrated by Fig. 1.1 [1]. According to [2], the global IC market was worth \$412.3 billion in 2019 and is expected to grow to \$502.94 billion by 2023, with analog components being present in more than 50% of the total IC shipments yearly. Besides, the strict time-to-market constraints and development costs make electronic systems' design challenging, being, therefore, fundamental to accelerate their development process as much as possible.

Plenty of EDA tools and design methodologies have been made available to cope with new capabilities offered by the integration technologies. However, there is still a considerable discrepancy between the analog and digital IC design tools. The gap between the number of existing EDA tools for digital and analog circuits is usually explained by the fact that the digital market is much larger, absorbing the available resources. It is also easier to express a digital system, which can be represented naturally in terms of Boolean expressions, whereas, on the analog side, their design is less systematic, more knowledge-based, and more heuristic [3]. Even though analog circuits only occupy a small fraction of these SoCs, they are responsible for most design errors and expensive redesigns/reruns. Therefore, economic pressure

**Mixed-Signal System-On-Chip**

Fig. 1.1 Contrast between analog and digital blocks' design effort [1]

has motivated the quest for better methodologies to accelerate analog design. The automation level for analog IC has improved in the last few years, a field of profound academic and industrial research activity producing significant advances. However, it is still far from the push-button stage, leading designers to keep exploring the solution space almost manually, as there are no standard plug-and-play EDA tools and methodologies to automate the analog IC design flow.

While most of this is true for analog base-band, on top of that, with predictions that more than half of new businesses will run on the internet-of-things (IoT) and advanced telecommunication broadbands, such as the 5th generation (5G), there will be an immense demand for devices and sensors, opening doors to advances in many areas. This has already led to an increase in the amount of data that is being continuously generated, resulting in new challenges within every part of the network. Consequently, there is high pressure in today's market for larger communication rates, extensive bandwidths, and ultralow-power consumptions. This is where RF ICs come in hand, playing a crucial role. However, RF IC design in deep nanometric integration technologies for both IoT and 5G is extraordinarily difficult, due to their high complexity and demanding performances. Some of the design difficulties lie in the wide range of frequencies and dynamic ranges involved, but also on:

- Their dependence on non-reliable models of passive devices;

- At gigahertz frequencies, there is a huge impact of layout parasitics;

- Their integration in deep nanometer technologies causes variability issues and non-idealities which have never been experienced in older technology nodes.

Avoiding costly redesign cycles and reducing post-fabrication tuning and compensation work on first-pass fabrication success became primary RF IC design objectives. Established computer-aided design (CAD) companies provide environments that allow circuit designers to carry this flow manually. Despite this, the classical trial and error method is no longer viable due to the high number of complex interactions leading to sub-optimal RF designs.

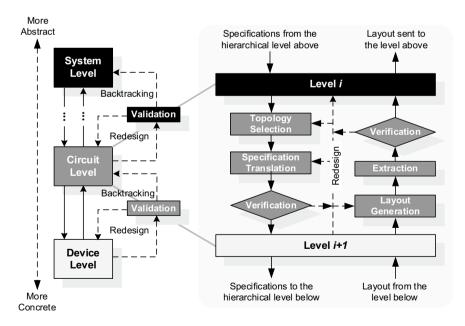

# 1.2 Analog IC Design Flow

Regarding the specific design flow of analog ICs, each designer/company may have its own. However, in [3], Gielen and Rutenbar standardized the steps that most designers take when designing an analog or mixed-signal IC, introducing the widely acknowledged design flow shown in Fig. 1.2. This flow consists of a series of top-down design steps repeated from the system to the device level and bottom-up layout generation and verification. Using a hierarchical top-down design methodology allows for performing system architectural exploration, achieving a better overall system optimization at a higher level of abstraction before starting more specific implementations at the circuit or device levels. With this, one can find problems earlier in the design flow, increasing the chances of first-time success with fewer time-consuming redesign iterations.

In this design flow, the number of hierarchy levels may vary according to the complexity of the system being designed, and although there are no overall accepted representations for the architectural design, the steps between two hierarchical levels are:

Fig. 1.2 Hierarchical levels and design tasks of analog design flow [4]

- Top-down electrical synthesis path, which includes topology selection, specification translation (or circuit sizing at the lowest level), and design verification;

- Bottom-up physical synthesis path, that includes layout generation and detailed design verification (after layout extraction).

In topology selection, the most appropriate circuit topology is determined to meet a certain number of specifications at the current hierarchy level. This topology can be chosen from a set of existing topologies or synthesized.

Specification translation is the step where the designer maps the high-level block specifications and, given a certain topology, maps them into individual specifications for each sub-blocks. Due to these sub-blocks being single devices at the lowest level, this task is narrowed down to circuit sizing. Before proceeding down in the hierarchy, specification translation is verified using simulation. At higher levels of the design flow, there is no device-level sizing available, which results in behavioral simulations. However, device sizing is available at lower levels (circuit and device level), and therefore, electrical simulations are used. Each block's specifications are passed to the following hierarchy level, and the whole process is repeated until the top-down electrical synthesis flow is completed.

To aid designers to overcome the many difficulties encountered in manual sizing of analog/RF IC blocks, several optimization-based sizing approaches emerged. These EDA tools use several algorithms that explore the design space effectively rather than iterating over designer-defined analytical equations. They can be used along with performance models that can capture several circuit characteristics of RF circuits. However, despite its increased computational effort, utilizing foundry-provided device models and a circuit simulator as an evaluation engine resulted in the most accurate and generally adopted approach. Most commercially available solutions that use the simulation-based architecture, e.g., Cadence's Virtuoso GXL [5] or MunEDA's DNO/GNO [6], still take a restrictive single-objective approach being used to semi-automate the manual sizing design process. Consequently, simulation-based techniques are a continuous research subject of the community to face the most recent design challenges.

After the top-down flow is completed at a certain level, the sizing obtained must be verified by generating the corresponding layout and testing its performance. If these prove to be satisfactory results, the design flow is finished. If not, a redesign is needed, repeating the previous steps or the complete flow.

## **1.3 Machine Learning and Analog IC Sizing**

ML is how a computer improves its capabilities by analyzing past experiences. This area of artificial intelligence (AI) has been chosen to solve problems in computer vision, speech recognition, and natural language processing, among others because it can be easier to train a system showing examples of what the output should be given a particular input than to anticipate all possible responses for all inputs. One of the most

used models nowadays is artificial neural networks (ANNs), and those are the models considered in this book. This technique has been cyclically picked-up and abandoned over the years, but a new trend emerged recently, called deep learning (DL), where much more complex networks are employed, yielding fascinating results in image processing, for example. They are also playing a role in the design automation of analog and RF integrated circuits ICs [7], being used on several fronts, e.g., modeling [8], mapping from devices' sizes to circuits' performances [9–11], mapping from specifications to the sizing [12], layout generation [13–17] or even fault testing [18].

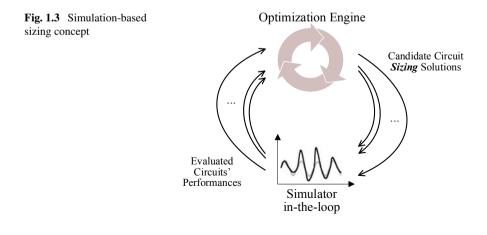

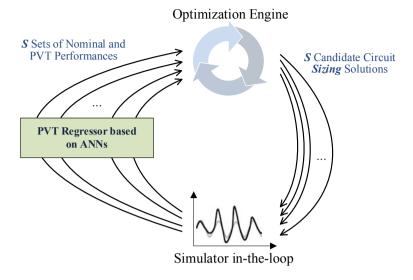

Analog IC performance evaluation is well established in the design flow. Furthermore, as stated in the previous section, this prominence of circuit analysis tools and methods led to simulation-based optimization as the most common method in both industrial [5, 6] and academic [19] environments. These automatic analog/RF IC sizing methods aim to find the best set of device sizes by iterating over tentative guesses and evaluating their impact on circuit performance, as shown in Fig. 1.3. This process is shown to produce usable designs, but it is still slow, and reuse usually involves new optimization runs. Some approaches have been made to use ML algorithms in analog IC sizing. However, most of the different approaches incorporating ML/DL concepts in the simulation-based sizing loop attempted to alleviate the simulator workload by building models that estimate the circuit performances, fully bypassing simulation.

From the analysis of state-of-the-art sizing tools available for analog IC and RF design automation described in Chap. 2 of this book, simulation-based sizing optimization tools are widely accepted approaches as they keep the solutions' accuracy high and assist in the design of modern blocks. For instance, in IoT applications, where the demand for ultralow-power (ULP) radios is significant, voltage-controlled oscillators (VCOs) are extremely relevant design blocks. Besides requirements such as phase noise and power consumption, the intrinsic tradeoff specifications, such as the frequency tuning range and frequency pushing due to the supply voltage variation, must be carefully considered in a practical design. Building a realistic analysis of the design tradeoffs is a challenging task, as multiple tuning modes deliver a

vast number of conflicting performance figures that need to be balanced. Adding further complexity, the impact of the process variations or parasitic layout structures turns the optimal balance of the design tradeoffs beyond human capabilities, which can only be solved with the assistance of automatic tools. Still, some challenges arise when designing complex RF circuit topologies using simulation-based sizing optimization:

- In some cases, the simulator is unable to converge to the guessed oscillation frequency, whereas in others, the simulation attempts to converge infinitely;

- The increase in simulation time of extracted netlists, as opposed to the pre-layout one, makes it harder to decide when to put a timeout on convergence attempts;

- An oscillation frequency guess must be provided for the steady state (SST) analysis. However, it is strongly correlated with the convergence of the analysis. Therefore, promising designs may still be lost without simulating multiple guesses.

# 1.4 Conclusion

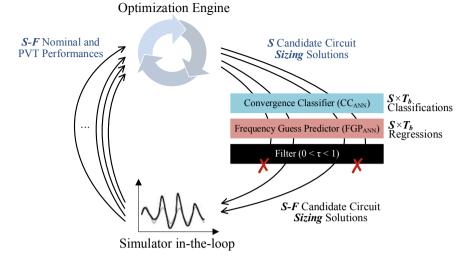

While the demand for new analog ICs for ever-increasing challenging specifications keeps building momentum, their design automation is still lacking and needs to be addressed. In this book, we explore how ML/DL can be used to increase the effectiveness of analog and RF automatic sizing. Chapter 3 proposes a methodology that disrupts the most recent trials of replacing the simulator in the simulation-based sizing with ML/DL by proposing two distinct ANN models. The 1st classifies the convergence of the circuit for nominal and PVT corners, bypassing solutions that will hardly produce valuable information for the evolutionary kernel, and the 2nd predicts the VCOs' oscillating frequencies for the conditions above. The convergence classifier ( $CC_{ANN}$ ) and frequency guess predictor (FGP<sub>ANN</sub>) are seamlessly integrated into the simulation-based sizing loop, as shown in Fig. 1.1, accelerating and complementing the optimization process. And, in Chap. 4, a PVT regressor that inputs the circuit's sizing and the nominal performances to estimate the PVT corner performances via multiple parallel ANNs greatly accelerates robust design. Two control phases prevent the optimization process from being misled by inaccurate performance estimates. Ultimately speeding up the analog/RF IC optimization-based sizing concept, complementing the simulation process with artificial neural networks, and reducing the simulator workload.

#### References

1. Lourenço N, Martins R, Horta N (2017) Automatic analog IC sizing and optimization constrained with PVT corners and layout effects. Springer, Berlin

- 2. The Business Research Company (2020) Integrated circuits global market report 2020. Technical report

- 3. Gielen GGE, Rutenbar RA (2000) Computer-aided design of analog and mixed-signal integrated circuits. Proc IEEE 88(12):1825–1854

- 4. Martins R, Lourenço N, Horta N (2012) Generating analog IC layouts with LAYGEN II. Springer briefs in applied sciences and technology. Springer, Berlin

- 5. Cadence (2019) Virtuoso analog design environment GXL. Retrieved from http://www.cad ence.com, Mar 2019

- 6. MunEDA (2019) WIKED<sup>TM</sup>. Retrieved from http://www.muneda.com, Mar 2019

- Afacan E, Lourenço N, Martins R, Dündar G (2021) Review: machine learning techniques in analog/RF integrated circuit design, synthesis, layout, and test. Integr VLSI 77:113–130

- Suissa A et al (2010) Empirical method based on neural networks for analog power modeling. IEEE TCAD 29(5):839–844

- 9. Wolfe G, Vemuri R (2003) Extraction and use of neural network models in automated synthesis of operational amplifiers. IEEE TCAD 22(2):198–212

- Alpaydin G, Balkir S, Dundar G (2003) An evolutionary approach to automatic synthesis of high-performance analog integrated circuits. IEEE Trans Evol Comput 7(3):240–252. https:// doi.org/10.1109/TEVC.2003.808914

- Liu H, Singhee A, Rutenbar RA, Carley LR (2002) Remembrance of circuits past: macromodeling by data mining in large analog design spaces. In: Proceedings 2002 design automation conference, pp 437–442

- Lourenço N et al (2019) Using polynomial regression and artificial neural networks for reusable analog IC sizing. In: 16th International conference on synthesis, modeling, analysis and simulation methods and applications to circuit design, pp 13–16, July 2019

- 13. Zhu K et al (2019) Genius route: a new analog routing paradigm using generative neural network guidance. In: Proceedings of the ICCAD

- 14. Guerra D, Canelas A, Póvoa R, Horta N, Lourenço N, Martins R (2019) Artificial neural networks as an alternative for automatic analog IC placement. In: International conference on SMACD, Lausanne, Switzerland, July 2019

- Gusmão A, Passos F, Póvoa R, Horta N, Lourenço N, Martins R (2020) Semi-supervised artificial neural networks towards analog IC placement recommender. In: IEEE International symposium on circuits and systems, Seville, Spain, Oct 2020

- Gusmão A, Horta N, Lourenço N, Martins R (2022) Scalable and order invariant analog integrated circuit placement with attention-based graph-to-sequence deep models. In: Expert systems with applications. Elsevier, Amsterdam

- Gusmão A, Póvoa R, Horta N, Lourenço N, Martins R (2022) DeepPlacer: a custom integrated OpAmp placement tool using deep models. In: Applied soft computing, vol 115. Elsevier, Amsterdam, 108188

- Andraud M, Stratigopoulos H, Simeu E (2016) One-shot non-intrusive calibration against process variations for analog/RF circuits. IEEE TCAS-I Regul Pap 63(11):2022–2035

- Gonzalez-Echevarria R et al (2017) An automated design methodology of RF circuits by using pareto-optimal fronts of EM-simulated inductors. IEEE Trans Comput Des Integr Circ Syst 36(1):15–26

# Chapter 2 Background and Related Work

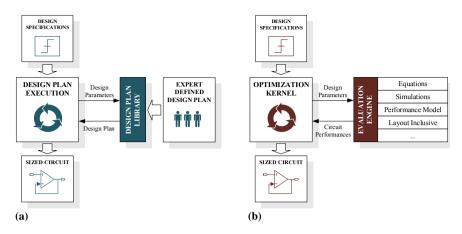

# 2.1 Knowledge-Based Sizing

As shown in Fig. 2.1a [1], knowledge-based sizing tools, e.g., IDAC [2] and BLADES [3], have attempted to systematize the design by making use of a design plan obtained from expert knowledge. These tools solve a pre-designed plan using circuit equations and a hard-coded design strategy to build component sizes that meet the performance requirements. While this approach presented satisfactory results for automatic analog IC sizing, being its main advantage of the short execution time. However, deriving the design plan is complex and requires a high development time. Additionally, the continuous effort required to keep the design plan up to date with the advances in fabrication technologies, the increase in the complexity of circuit topologies, and the fact that the results obtained are not simulator-accurate make this approach suitable only as a first-cut design.

# 2.2 Optimization-Based Sizing

Aiming for optimality, the next generation of sizing tools has applied optimization techniques to analog/RF IC sizing, which can be further classified into equation-based or simulation-based when considering the method used to evaluate the circuit's performance, as illustrated in Fig. 2.1b [1].

# 2.2.1 Equation-Based Evaluation

Equation-based methods use analytic design equations to describe the circuit performance, and then, to resolve the degrees of freedom, tools such as OPASYN [4]

Fig. 2.1 Automatic circuit sizing methods: a knowledge-based and b optimization-based [1]

and CADICS [5] were used. Since the design equations had to be deduced by hand, the symbolic simulator ISAAC [6] was developed to automatically produce design equations used to evaluate the circuit performance in a relatively less complex process. This process reduces the setup time when optimizing new circuit topologies. Nonetheless, similar to knowledge-based sizing, the problem of using these methods is still mapping design characteristics by analytic equations, which is not straightforward. The approximations introduced in the equations result in poor accuracy when compared with the circuit simulator.

# 2.2.2 Simulation-Based Evaluation

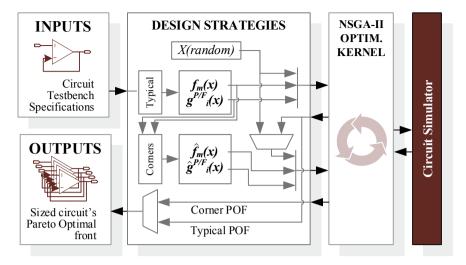

Simulation-based optimization is the most prevalent method in both industrial [6, 7] and academic environments since designers prefer to avoid the risks of estimation errors in equation-based performance approximation. These simulation-based methods use an off-the-shelf circuit simulator to evaluate the circuit's performance. The main advantage of these approaches over the equation-based evaluation is its improved generalization capabilities, still, due to the long execution times required for some SPICE-based circuit evaluations and since a considerable number of simulations (hundreds to thousands) are required to reach the desired solutions, it may result in a time-consuming optimization process. One example of this approach was introduced in [8], where an analog IC design automation environment called AIDA implements a design flow from a circuit-level specification to a physical layout description. AIDA was a combination and integration of two in-house tools, GENOM-POF [9], responsible for the circuit synthesis and whose architecture is illustrated in Fig. 2.2, and, LAYGEN II [10], the AIDA's layout generator.

Fig. 2.2 GENOM-POF architecture based on the NSGA-II and using circuit simulator [8]

GENOM-POF was based on the multi-objective evolutionary optimization kernel NSGA-II [11] and used the industry standard circuit simulator Mentor Graphics' HSPICE as an evaluation engine to address robust design requirements, e.g., corner analysis. Corner analysis is one of the most used techniques for analog IC design centering. It corresponds to a worst-case approach in which a sizing solution for a given circuit topology is simulated over multiple combinations of parameter variations, such as process, power supply, or temperature. In GENOM-POF, the designer's inputs were the circuit and its testbench in the form of HSPICE netlist(s). These netlists must have, as parameters, the optimization variables and must include a method to measure the circuit's performance. The designer also had to define the desired range of the optimization variables, design constraints, and optimization objectives.

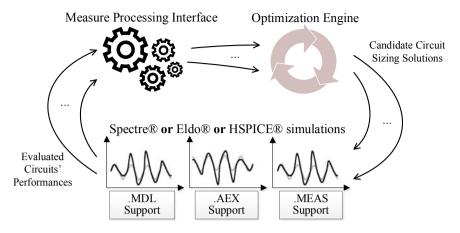

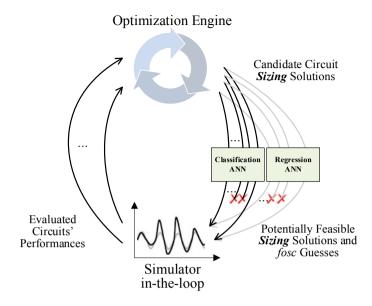

In the past few years, RF IC design has exploited this concept of simulationbased sizing [12–18]. Regarding AIDA-C [19], an enhanced version of GENOM-POF whose general flow is illustrated in Fig. 2.3, represents a generic number of candidate circuit sizing solutions, P, proposed by the optimization engine, where each one is a series of possible combinations of design variables. It is an iterative process, where in each iteration, the framework simulates the several test benches, K, affected by each sizing of P, to extract the desired measures. The most widely adopted commercial circuit simulators are supported in this process, such as Cadence's SPECTRE, Synopsys' ELDO, or Mentor Graphics' HSPICE. Due to a measure-processing interface, it is possible to combine measures from different test benches into composed expressions, which can be used as targets for the constrained multi-objective optimization problem.

Fig. 2.3 Design flow of a multi-test bench analog and RF IC sizing optimization [19]

### 2.3 Machine Learning in Simulation-Based Evaluation

As each simulation made within an optimization-based loop may be a timeconsuming process, an effort has been made to develop techniques that reduce the workload of the simulator, most of them focused on ML. ML is a subset of artificial intelligence, even though the latter aims to build complex decision systems and the former focuses on the statistical properties of data [20]. In his essay on probability theory, Thomas Bayes proposed several theorems [21] that laid the theoretical foundations for statistical learning and is the cornerstone for some early ML techniques, such as naive Bayes or Markov chains. In 1951, the first artificial neural machine was proposed. However, artificial neural networks (ANNs) only began to receive more attention from the community with Frank Rosenblatt's perceptron [22] and back-propagation [23] in 1958 and 1986, respectively, wherein the latter principles of dynamic programming were introduced. In the meantime, many other accomplishments have been achieved, and today there are a vast number of different ML techniques for solving classification and regression tasks.

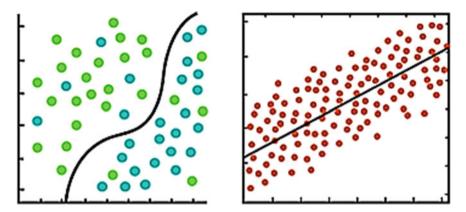

In a classification problem, the main goal is to categorize data correctly. A typical example is the email spam filter which assigns incoming emails to the "spam" or "not-spam" categories. In a regression problem, the system's primary goal is to describe one or more continuous-value dependent variables as functions of the data observations. An example of regression is predicting house prices given the house's features (size, the number of rooms, location, etc.). A visual comparison between these two problems is shown in Fig. 2.4.

Fig. 2.4 Classification (left) versus regression (right) problems [25]

# 2.3.1 Types of Supervision

A critical characteristic of all ML systems is their ability to adapt correctly to new, previously unseen data and avoid overfitting the training data. Overfitting occurs when the system learns the detail and noise in the training data to the extent that it negatively impacts the performance of the system on new data, affecting its generalizing capabilities [20, 24]. Another attribute of an ML system is the amount and type of supervision. The following subsections refer to the different supervision categories in which an ML system can be categorized.

#### 2.3.1.1 Supervised Learning

For these models, the dataset used must have some observations and the expected results, called labels. The labels can further divide this method into two problemsolving techniques: classification and regression. As stated, a classification problem is when the output variable is part of a group, for instance, "dog" or "not dog," whereas regression is a case where the output variable is a real value, such as the cost of a house. Some examples of important supervised learning algorithms are linear regression, logistic regression, decision trees, support vector machines (SVMs), and ANNs.

#### 2.3.1.2 Unsupervised Learning

The training uses data that has not been labeled for these models, aiming to create models that can draw inferences from datasets to describe hidden structures. Unsupervised learning is particularly suitable for problems such as clustering or association. A clustering problem is characterized by disclosing the inherent groupings in

the data, for instance, grouping people based on their age, whereas an association problem aims to discover relations rules within the data, such as people who buy X also tend to buy Y. Some examples of relevant algorithms are principal component analysis, K-means, and mixture models.

#### 2.3.1.3 Semi-supervised Learning

Semi-supervised learning is the third category that falls between supervised learning and unsupervised learning. Its training data combines a small amount of labeled data with a large amount of unlabeled data, and the system is trained with a combination of supervised and unsupervised algorithms. Some algorithm examples are autoencoders and deep belief networks.

## 2.3.2 Simulation-Based Sizing Enhanced with SVMs

With the recent technology advancements, the use of macro models such as ANNs or SVMs introduced another type of optimization-based sizing, designated numericalmodel based. Given the models' prediction speed, by using these tools, one can reduce the high simulation times of the simulator loop by aiding the simulator in certain tasks or, in a more drastic way, by completely replacing the simulator.

Starting with SVMs, which is a supervised learning algorithm for data separation, making use of linear combinations to produce a boundary that maximizes the margin between classes. This algorithm is especially interesting if the data is linearly separable, as for nonlinear patterns, a kernel trick is used, allowing the SVM to create this boundary in a higher dimension hyperplane.

In [1], an SVM classifier is used to enhance the multi-objective IC sizing optimization process. The previously presented analog IC sizing tool, GENOM-POF, was used to demonstrate the methodology. The SVM is used to create feasibility models that diminish the design search space during the optimization process, reducing the number of required evaluations. This approach was validated using benchmark examples consisting of two different circuits, a single-ended folded cascode amplifier, and a fully differential telescopic amplifier. The functional feasibility regions used to train the feasibility model were defined by functional constraints, where the training data used to train the model was obtained using a design of experiments. The sampled points obtained were sorted into 3 classes, feasible, quasi-feasible, and infeasible. Finally, the evaluation was made, where the model classifies the individuals based on their classes, discarding the unfeasible ones. The results showed that the models had absolute gains ranging from 10 to 20% in terms of the overall reduction in the number of evaluations required. As the electrical simulation is more time-consuming than the SVM model evaluation, it allows an efficient diminishing of the design search space.

In [26], an SVM is also used to identify the feasibility of the design space of analog circuits to reduce a large amount of the entire design space, sampling only the points considered feasible and their neighbors. After choosing the proper parameters of the SVM, the resulting model may reach 100% accuracy on the training data. So, the difficulty relies on the generalization capability when facing an independent validation data set. To tackle this issue, three accuracy metrics were presented, i.e., overall accuracy, percentage of false negatives, and percentage of false positives. These metrics are presented in Eqs. (2.1), (2.2), and (2.3), respectively:

$$P_{t} = \frac{Number of correctly classified samples}{Number of samples in the validation set}$$

(2.1)

$$P_{fn} = \frac{Number \ of \ false \ negatives}{Number \ of \ positives \ in \ the \ validation \ set}$$

(2.2)

$$P_{fp} = \frac{Number of \ false \ positives}{Number of \ predicted \ positives}$$

(2.3)

Two circuits were used as a case study to validate this method: an operational transconductance amplifier and a low-voltage double-balanced mixer. With discarding the predicted negative values, the coverage of the feasibility design space was consistently above 99% for both circuits, and the rate of feasible designs that were excluded from being sampled was in the order of  $10^{-4}$ . Finally, the computational time was also reduced, where the results show between 59 and 71% reduction when compared with previous approaches. The problem with using SVMs is that tuning hyper-parameters and selecting the correct kernel is quite challenging. SVMs also have degraded performance when faced with large datasets and a higher number of features.

### 2.3.3 Simulation-Based Sizing Enhanced with ANNs

Today, ANNs are pretty popular in ML due to the increased data and computing power available. These two factors prevented researchers from using them altogether in academic settings in the past. However, nowadays, with fast-processing computers, ANNs can be found in image processing, speech recognition, and other areas where large amounts of data are available. They are systems based on the human brain, copying how we learn and make decisions. These networks are composed of an input and an output layer and one or more hidden layers. Each of these layers is a combination of neurons, where the input layer is where the data is fed to the network and the output layer is where the algorithm results are obtained.

The advantages of using ANNs are their high performance, capability to solve problems impossible for humans, an excellent algorithm for regression and classification problems, and ability to handle large amounts of data. Some disadvantages are their black-box nature (i.e., it is difficult for researchers to completely understand why the algorithm behaves a certain way because of how the numerical values are produced), the long time to train the model, and the large amount of data required. Nonetheless, ANNs have been proven to build effective end-to-end ML systems, which can also be used for the design automation of analog and RF ICs [27–29]. These may span from modeling [30], synthesis [31], layout generation [32–37], or even fault testing [38].

In [39], a neural network-based methodology is used to estimate the performance parameters of different CMOS operational amplifier topologies. To obtain the efficiency and accuracy of the resulting performance models, these were used in a genetic algorithm-based circuit synthesis system. The performance parameters of the synthesized circuits were validated by SPICE simulations and compared with the ones predicted by the ANN models. Training data of the model was directly generated through SPICE simulations to provide accurate and reliable data to the system. The ANN's architecture had only one hidden layer, with its number of neurons ranging from 8 to 13. However, its generalization capabilities were limited, as in some performances predicted by the model, the test error reached 60%.

This approach proved to be much faster when compared to the traditional SPICE simulation. The genetic algorithm, using the ANN models, was executed 10,000 times to produce 8 performance parameters, each obtained through a different iteration. Through SPICE simulation, each of these iterations would require 2 s to complete, which would total about 44 h  $(10,000 \times 2 \times 8)$  for all configurations. The execution time using ANN models was about 80 s for all configurations, representing a speed-up factor of  $2000 \times$ . Beyond some of the higher reported errors, the models also proved to be capable of capturing nonlinear behavior of the performance characteristics of a circuit which requires a large number of simulations, but in the end, the effort is justified when considering the reusability of the models in other amplifier topologies.

In [40], an ANN with two hidden layers is used to replace the SPICE simulator. Multi-objective optimization is frequently used in analog sizing to reveal the tradeoffs of the design specifications with the help of Pareto optimal fronts (POFs). A rough POF can be found in a reasonable time with multi-objective optimization, but the high-quality ones require a large amount of simulator iterations, resulting in long synthesis periods. In this paper, a method is presented to speed-up this process. After a multi-objective optimization phase to obtain a, designated, low-quality POF, the process switches to a faster single-objective optimization to complete the POF making it smoother and more continuous. At this phase, the SPICE simulator was also replaced by an ANN, reducing the synthesis time even further. The training data for the ANN was obtained from the multi-objective optimization phase.

This method was applied to the design of two circuits, a two-stage amplifier, and a folded cascode operational transconductance amplifier to validate this tool. For the first circuit a speed-up factor of about  $29.7 \times$  was obtained, which translates to a 96.6% time reduction, with a maximum error of 0.44%. As for the second circuit, a speed-up factor of 28.3 was obtained, representing a 96.4% time reduction, with a maximum error of 1.55%.

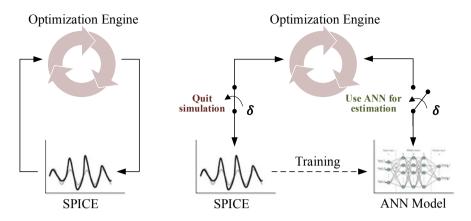

Fig. 2.5 a General flow of simulation-based synthesizer and b modified flow with ANN as performance estimator [40]

In [41], a similar method is used to accelerate a simulation-based circuit synthesizer using ANNs to determine circuit performances instead of a SPICE simulator. Instead of training the ANN with simulation data beforehand and simply replacing the simulator with the trained ANN, the simulation-based synthesizer is left unchanged for some generations of the optimization loop, and only after a period the ANN replaces the SPICE simulator. Unlike other conventional algorithms, all the data generated in the first phase is used as training data for the ANN instead of being discarded. The proposed circuit synthesizer flow is shown in Fig. 2.5. Since the training data acquisition step consumes a significant amount of time and is necessary for every new topology to be treated, the main innovation of this approach is that no separate data acquisition step to train the ANNs is required. Therefore, the flow can be used for every new topology without losing generality for all analog circuits.

This method was applied to the circuit synthesis phase of two circuits, a singlestage amplifier, and a folded cascode operational transconductance amplifier. With only the SPICE simulator, the circuit sizing of the single-stage amplifier took 4.92 h to complete, where the optimizer was executed for 100 generations. With ANNs replacing the simulator after the first 20 generations, the execution time was reduced by 64.8%, corresponding to a speed factor of  $2.84 \times$ , with errors below 1%. For the folded cascode amplifier, which presents a higher complexity, the original optimizer took 400 generations and 22.58 h to complete the circuit sizing. The best time reduction obtained with ANNs was 50.3% with errors below 1%, where the ANN replaced the simulator after 155 generations.

All these approaches to reduce the execution time of optimization-based sizing use ANNs to replace or complement the circuit simulator. The execution time is greatly reduced by avoiding time-consuming circuit simulations. However, in [39, 42], at later stages of the optimization, the circuit simulator is re-established to recover the accuracy lost. Furthermore, the ANN models are trained over the entire design space, which spends valuable resources modeling and evaluating large regions of unusable

|                             |                   | 8             |                  |                              |

|-----------------------------|-------------------|---------------|------------------|------------------------------|

| Reference                   | Speedup<br>factor | Maximum error | Number of layers | Method                       |

| Wolfe and Vemuri<br>[39]    | $\approx 2000$    | 60%           | 3                | Complement/Replace simulator |

| Çakıcı et al. [40]          | 29.7              | 1.55%         | 3                | Replace simulator            |

| İslamoğlu et al. [41]       | 2.8               | 0.77%         | 4 and 5          | Semi-replace simulator       |

| Hakhamaneshi et al.<br>[44] | n/r               | n/r           | 4                | Replace simulator            |

| Alpaydin et al. [42]        | n/r               | n/r           | 3                | Complement simulator         |

| Liu et al. [43]             | n/r               | ≈ 10,000%     | 3                | Replace simulator            |

Table 2.1 Speeding-up simulation-based sizing with ANNs overview

n/r-not reported

design combinations. In [43], the ANNs were also trained to replace the simulator, but the previous issue is somewhat addressed by applying data mining techniques to build a model that captures only significant regions of the performance space visited during automatic synthesis.

In [44], deep neural networks (DNNs) boost the optimizer's sample efficiency. With the use of an oracle, a comparison is made between two designs, in terms of each design variable, as a method to select which of the two designs is likely to have better performance figures in advance. Since DNNs are especially good at approximating complex functions and have a good generalization to unseen samples, a DNN model is derived to behave as an oracle, which is in fact a simulator. This discriminator achieves at least two orders of magnitude in sample efficiency, representing a considerable reduction in the number of simulations required. A summary of these tools is shown in Table 2.1.

## 2.4 Other ML/DL Efforts on Analog/RF Sizing

This section overviews different ML applications in the analog/RF IC sizing domain.

## 2.4.1 Predicting Sizing from Performances

Using ANNs to find device sizing in analog IC proved to be feasible. These methods learn and output a candidate circuit sizing when asked for target specifications [45, 46]. In [31], an ANN is developed to give the channel widths of all the transistors in a circuit when the designer gives the desired output specifications. The training phase data was performed with different SPICE parameters from the ones used in the test data in order to show the ability to give the transistor sizes of a circuit

for new untrained technology, having no dependency on the SPICE parameters. As a method of validation, two circuits were used, current mirrors and a CMOS differential amplifier. For the first one, a general regression neural network was used, and the results showed that it could estimate the current mirror's transistor sizes for new technologies with 94% accuracy. For the second one, a multilayer perceptron was used, and its results had an accuracy of 90%.

In [47], to produce the sizing for a low noise amplifier, several ANNs are put in sequential order, having as input the intended performance. The results have shown good prediction accuracy. However, the training and tuning of such a model have proven to be exceedingly tricky. While only 277 handmade sizing solutions were used for the training phase, an outer loop was still required to define the model's hyperparameters, reflected in a train of over 5 h on such a short dataset. In [48], the sizing for an amplifier is also predicted using ANNs when given its specifications. However, in this work, the model and training phases are different since the test was only performed on ten samples from the original dataset, and no evaluation is made on the performance and usability of the model for unknown target specifications.

## 2.4.2 Reinforcement Learning

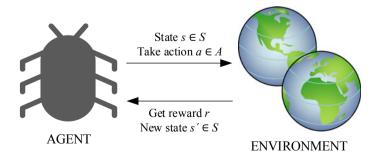

Reinforcement learning (RL) aims to develop an agent that learns how to behave in a particular environment where the only feedback is the reward of its actions. This interaction between the agent and environment is depicted in Fig. 2.6. The agent's primary goal is to maximize the notion of cumulative reward regarding its actions. These systems can teach robots to learn motor skills [49] or master complex board games like chess or Go [50].

RL can also be used in analog/RF sizing. In [51], an agent learns from trial and error how to behave like a circuit designer evolving to discover circuit sizes that satisfy the performance specifications finally. Another instance where RL is used for sizing is in [52], a tool named AutoCkt, an ML optimization framework trained using deep RL, that is capable of finding post-layout circuit parameters for a particular parameter

Fig. 2.6 Interaction between agent and environment

specification and can also acquire knowledge about the entire circuit design space using a sparse subsampling technique.

This method uses models to make a sequence of decisions. The agent observes and interacts with an uncertain, potentially complex environment by selecting and executing actions, following a trial-and-error approach, and getting rewards or penalties according to what action it performs. The agent is trained to learn a policy that maximizes the expected outcome of the actions over time. These methods have been used to play complex board games or, for instance, in an autonomous vehicle to put safety first or minimize ride time. This method has been used in alternating current optimization in [51–53]. With deep learning, an agent is trained, not needing previous knowledge about optimizing circuits.

#### 2.5 Case Study

To justify the motivation behind the developments proposed in this book, and to demonstrate how a time-consuming simulation step may hinder an effective optimization-based synthesis, a case study is introduced within this section, which will be explored in the following chapters.

### 2.5.1 Dual-Mode Class C/D VCO

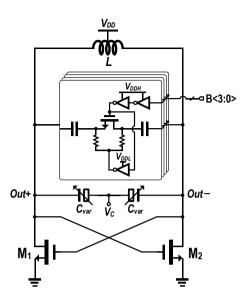

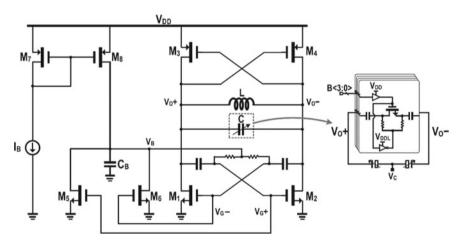

The development of the proposed methodologies will be tested on the sizing of a complex dual-mode class C/D voltage-controlled oscillator (VCO), whose schematic is presented in Fig. 2.7 and whose optimization was firstly described in [54]. In that work, instead of achieving the desired performance parameters with sequential single-objective optimizations, a single many-objective sizing optimization, described as "everything-at-once" optimization, is proposed to find the best performance boundaries. The circuit simulator performed a multi-process corner analysis and the optimization, taking into account two different tuning modes,  $b_{0000}$  and  $b_{1111}$ . The results pushed the circuit to its performance limits, reducing to almost half of the power consumption of the original design, and showing its potential for ultralow-power with more than 93% reduction. In the optimizations carried, there were 28 optimization variables that affected the sizing of 43 devices. The full list can be found in Table 2.2.

A total of 18 performance figures were considered from 7 different testbenches and the optimizations were performed with populations of 512 elements optimized through 200 generations only. Each optimization took approximately 50 h to complete in an Intel-Xeon CPU E5-2630-v3@2.40 GHz with 64 GB of RAM workstation using eight cores for parallel evaluation, i.e., more than 2 days. Nonetheless, a complete process, voltage and temperature (PVT) corners optimization of this circuit is desired, Fig. 2.7 Dual-mode Class C/D VCO [54]

Table 2.2 Optimization variables for the dual-mode class C/D VCO

| Variable               | Units | Min. | Grid | Max. |

|------------------------|-------|------|------|------|

| ind_radius             | μm    | 15   | 5    | 90   |

| ind_nturns             | -     | 1    | 1    | 6    |

| ind_spacing            | μm    | 2    | 1    | 4    |

| ind_width              | μm    | 3    | 1    | 30   |

| mccl, m1l              | nm    | 60   | 20   | 240  |

| mccw, m1w              | μm    | 0.6  | 0.2  | 6    |

| mccnf, m1nf            | -     | 1    | 1    | 32   |

| mccm                   | -     | 1    | 1    | 100  |

| moscapw                | μm    | 0.4  | 0.2  | 3.2  |

| moscapl                | μm    | 0.2  | 0.2  | 3.2  |

| mimvw, mimvl, mim1w    | μm    | 2    | 0.2  | 20   |

| r11, r21, r31, r41     | μm    | 1    | 0.2  | 10   |

| r1m, r2m, r3m, r4m     | _     | 1    | 1    | 20   |

| nfn1, nfn2, nfp1, nfp2 | -     | 1    | 1    | 100  |

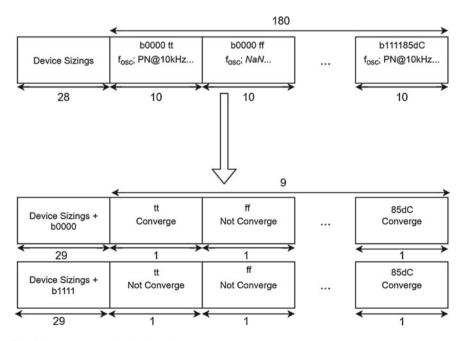

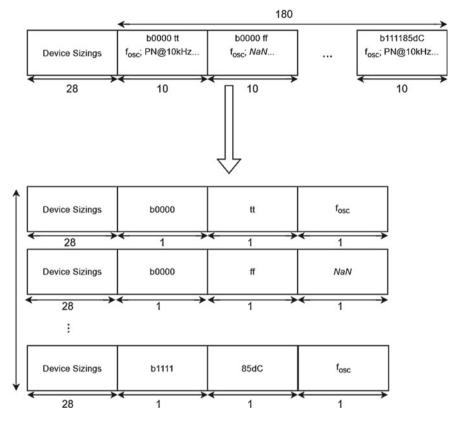

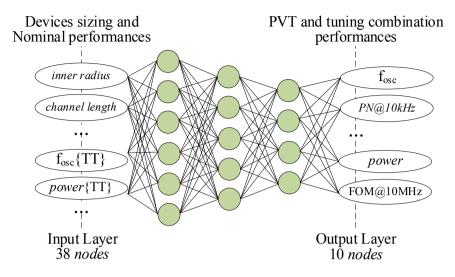

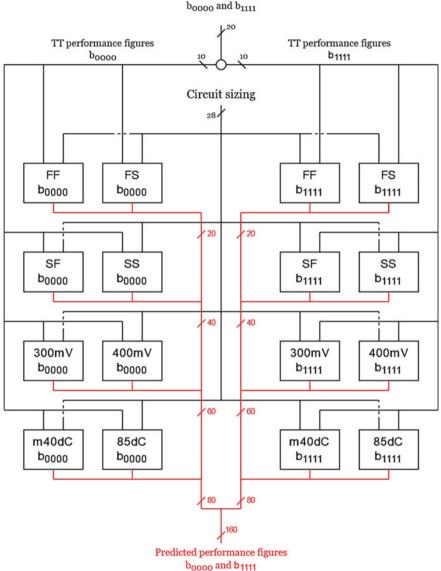

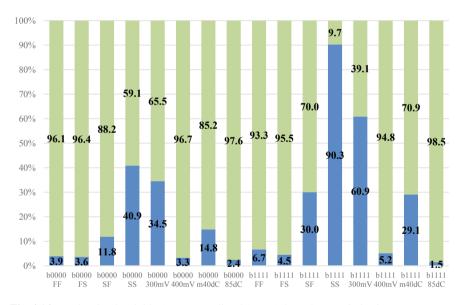

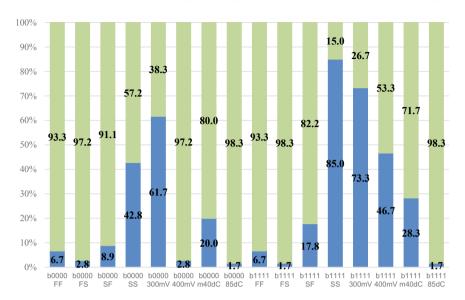

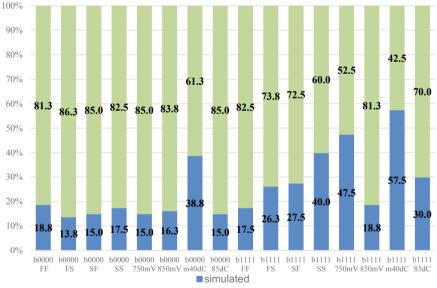

which will expand that number of required simulations. Namely, 9 different testbench variations will be considered (TT, FF, FS, SF, SS, 300mV, 400mV, m40dC and 85dC), that produce 10 different performance figures each, and, due to the worst-case tuning range optimization where two tuning modes are evaluated,  $b_{0000}$  and  $b_{1111}$ , resulting in each sizing being simulated 18 times and providing a total of 180 simulated

| Name           | Process | Voltage (V) | Temperature (°C) |

|----------------|---------|-------------|------------------|

| Typical (TT)   | TT      | 0.35        | 25               |

| Fast-Fast (FF) | FF      | 0.35        | 25               |

| Fast-Slow (FS) | FS      | 0.35        | 25               |

| Slow-Fast (SF) | SF      | 0.35        | 25               |

| Slow–Slow (SS) | SS      | 0.35        | 25               |

| 300mV          | TT      | 0.3         | 25               |

| 400mV          | TT      | 0.4         | 25               |

| m40dC          | TT      | 0.35        | -40              |

| 85dC           | TT      | 0.35        | 85               |

| Table 2.3  | List of TT and |

|------------|----------------|

| PVT testbe | enches for the |

| dual-mode  | class C/D VCO  |

| Table 2.4 List of           |

|-----------------------------|

| performances considered for |

| the dual-mode class C/D     |

| VCO in TT and PVT corners   |

| Measure          | Units  | Description                |

|------------------|--------|----------------------------|

| f <sub>osc</sub> | GHz    | Oscillation frequency      |

| PN@10 kHz        | dBc/Hz | Phase noise at 10 kHz      |

| PN@100 kHz       | dBc/Hz | Phase noise at 100 kHz     |

| PN@1 MHz         | dBc/Hz | Phase noise at 1 MHz       |

| PN@10 MHz        | dBc/Hz | Phase noise at 10 MHz      |

| Power            | mW     | Power consumption          |

| FOM@10 kHz       | dBc/Hz | Figure-of-merit at 10 kHz  |

| FOM@100 kHz      | dBc/Hz | Figure-of-merit at 100 kHz |

| FOM@1 MHz        | dBc/Hz | Figure-of-merit at 1 MHz   |

| FOM@10 MHz       | dBc/Hz | Figure-of-merit at 10 MHz  |

performance figures. The full list of testbench variations can be seen in Table 2.3 and the list of performances in Table 2.4.

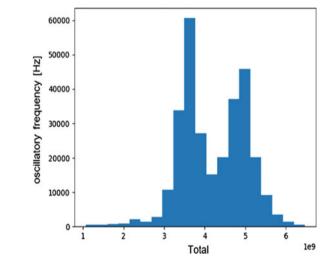

# 2.5.2 Dataset Generation

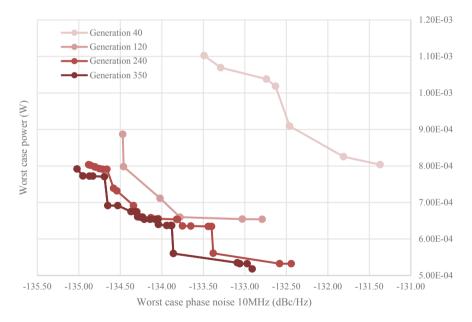

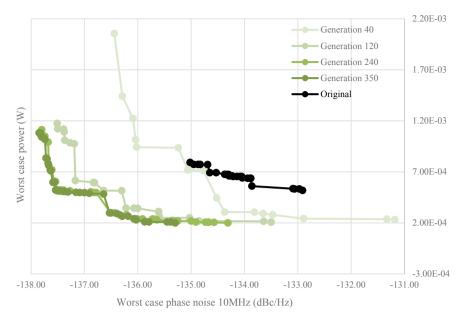

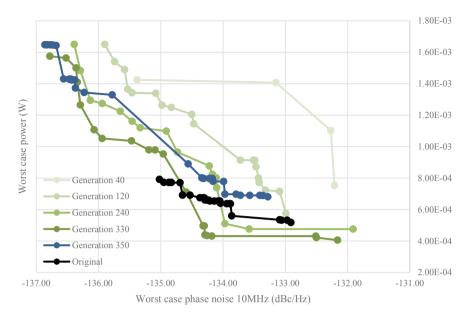

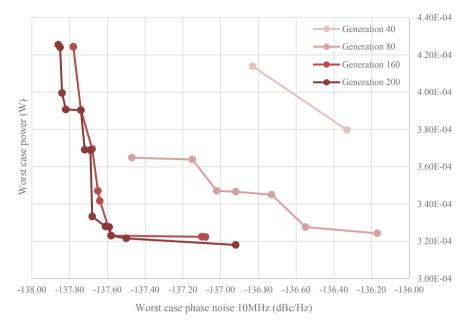

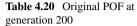

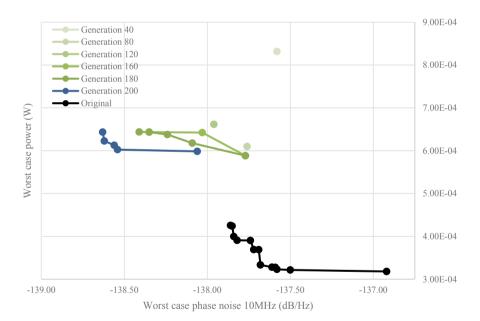

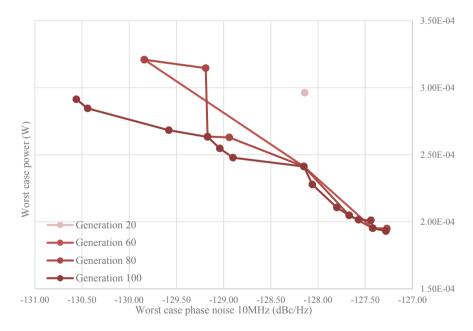

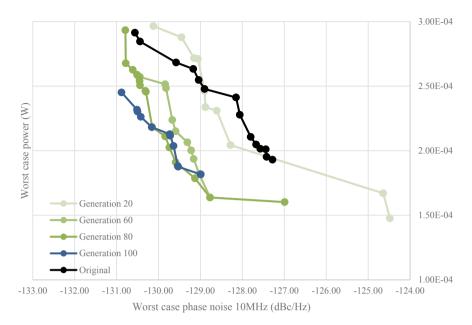

To generate the dataset an optimization was conducted in order to minimize both power and phase noise at 10 MHz in both tuning modes, while imposing constraints on other 7 measured performances for each testbench, i.e., in all combinations of PVT corners and tuning modes. These optimization constraints and objectives are shown in Table 2.5. The optimization was executed through a total of 350 generations and took a total of 612 h to complete and resulted in a total of 27 sizing solutions. In Fig. 2.8 is shown the POF evolution of the original optimization which contains the best sizing solutions throughout the generations, and, in Table 2.6 the values of the final POF obtained at generation 350 are shown.

| Tuning mode              | Measure          | Testbenches | Units  | Opt. constraint | Opt. objective |

|--------------------------|------------------|-------------|--------|-----------------|----------------|

| $b_{0000}$               | f <sub>osc</sub> | All         | GHz    | $\geq 4.8$      |                |

|                          | PN@10 kHz        | All         | dBc/Hz | ≤ - 49          |                |

|                          | PN@100 kHz       | All         | dBc/Hz | ≤ - 76          |                |

|                          | PN@1 MHz         | All         | dBc/Hz | $\leq -98$      |                |

|                          | PN@10 MHz        | All         | dBc/Hz | $\leq -119$     | Minimize       |

|                          | Power            | All         | mW     | n/d             | Minimize       |

|                          | FOM@10 MHz       | All         | dBc/Hz | $\geq -180$     |                |

| <i>b</i> <sub>1111</sub> | f <sub>osc</sub> | All         | GHz    | <i>≤</i> 3.9    |                |

|                          | PN@10 kHz        | All         | dBc/Hz | $\leq -55$      |                |

|                          | PN@100 kHz       | All         | dBc/Hz | $\leq -82$      |                |

|                          | PN@1 MHz         | All         | dBc/Hz | ≤ - 103         |                |

|                          | PN@10 MHz        | All         | dBc/Hz | ≤ - 124         | Minimize       |

|                          | Power            | All         | mW     | n/d             | Minimize       |

|                          | FOM@10 MHz       | All         | dBc/Hz | $\geq -180$     |                |

Table 2.5 Optimization constraints and objectives

Fig. 2.8 POF evolution throughout the original optimization

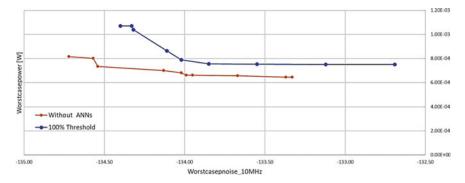

| Worst case<br>phase noise<br>10 MHz<br>(dBc/Hz) | Worst case<br>power (mW) | Worst case<br>phase noise<br>10 MHz<br>(dBc/Hz) | Worst case<br>power (mW) |

|-------------------------------------------------|--------------------------|-------------------------------------------------|--------------------------|

| - 135.02                                        | $7.918 \times 10^{-1}$   | - 134.14                                        | $6.539 \times 10^{-1}$   |

| - 134.95                                        | $7.727 \times 10^{-1}$   | - 134.08                                        | $6.537 \times 10^{-1}$   |

| - 134.87                                        | $7.722 \times 10^{-1}$   | - 134.06                                        | $6.537 \times 10^{-1}$   |

| - 134.83                                        | $7.722 \times 10^{-1}$   | - 134.05                                        | $6.536 \times 10^{-1}$   |

| - 134.69                                        | $7.707 \times 10^{-1}$   | - 134.04                                        | $6.397 \times 10^{-1}$   |

| - 134.65                                        | $6.914 \times 10^{-1}$   | - 133.94                                        | $6.369 \times 10^{-1}$   |

| - 134.53                                        | $6.914 \times 10^{-1}$   | - 133.89                                        | $6.369 \times 10^{-1}$   |

| - 134.37                                        | $6.749 \times 10^{-1}$   | - 133.88                                        | $6.368 \times 10^{-1}$   |

| - 134.32                                        | $6.746 \times 10^{-1}$   | - 133.86                                        | $5.601 \times 10^{-1}$   |

| - 134.30                                        | $6.746 \times 10^{-1}$   | - 133.09                                        | $5.348 \times 10^{-1}$   |

| - 134.29                                        | $6.605 \times 10^{-1}$   | - 133.06                                        | $5.323 \times 10^{-1}$   |

| - 134.26                                        | $6.598 \times 10^{-1}$   | - 132.97                                        | $5.322 \times 10^{-1}$   |

| - 134.23                                        | $6.596 \times 10^{-1}$   | - 132.91                                        | $5.178 \times 10^{-1}$   |

| - 134.21                                        | $6.539 \times 10^{-1}$   |                                                 |                          |

| Table 2.6   | Final solutions of  |

|-------------|---------------------|

| the origina | l POF at generation |

| 350         |                     |

# 2.6 Conclusion

In this chapter, different methods used in circuit optimization sizing were introduced and compared regarding the evaluation engine used, emphasizing simulationbased sizing. Using a simulator as the evaluation engine is the most widely accepted approach, with its main advantages being its generality and easy-and-accurate model. The main problem with this method is how time-consuming it may become when the SPICE-like simulation times increase. In recent works, the use of ML tries to address and solve this problem by often introducing SVM and ANNs into the optimization phase by either replacing or complementing the circuit simulator.

#### References

- Lourenço N, Martins R, Barros M, Horta N (2013) Analog circuit design based on robust POFs using an enhanced MOEA with SVM models. In: Fakhfakh M, Tlelo-Cuautle E, Castro-Lopez R (eds) Analog/RF and mixed-signal circuit systematic design. Lecture notes in electrical engineering, vol 233. Springer, Berlin

- Degrauwe M et al (1987) IDAC: an interactive design tool for analog CMOS circuits. IEEE J Solid-State Circ 22(6):1106–1116

- 3. El-Turky F, Perry EE (1989) BLADES: an artificial intelligence approach to analog circuit design. IEEE Trans Comput Aided Des Integr Circ Syst 8(6):680–692

- 4. Koh H, Sequin CH, Gray PR (1990) OPASYN: a compiler for CMOS operational amplifiers. IEEE Trans Comput Aided Des Integr Circ Syst 9(2):113–125

- 5. Jusuf G, Gray P, Sangiovanni-Vincentelli A (1990) CADICS—cyclic analog-to-digital converter synthesis. In: Proceedings of ACM/EEEE ICCAD, pp 286–289

- Gielen G, Walscharts H, Sansen W (1989) ISAAC: a symbolic simulator for analog integrated circuits. IEEE J Solid-State Circ 24(6):1587–1597

- Cadence (2019) Virtuoso analog design environment GXL. [Online]. Available: http://www. cadence.com. Accessed: 15 May 2019

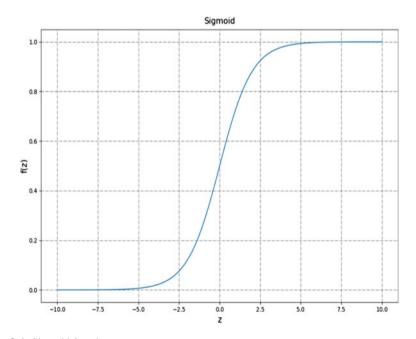

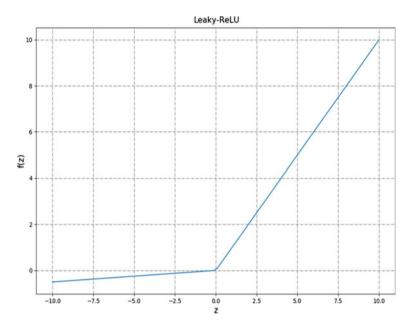

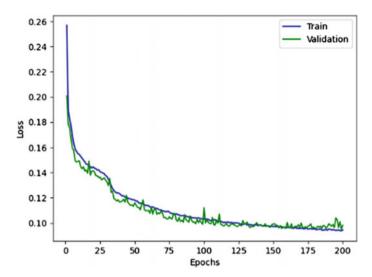

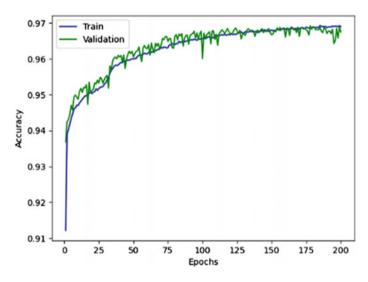

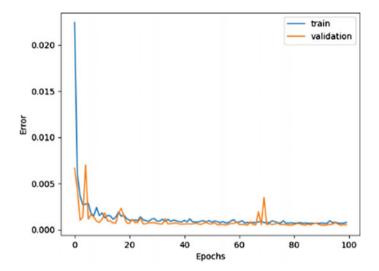

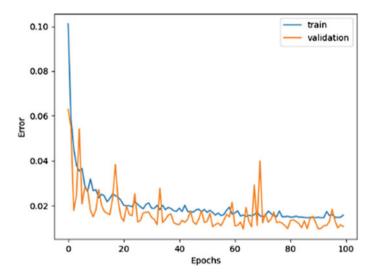

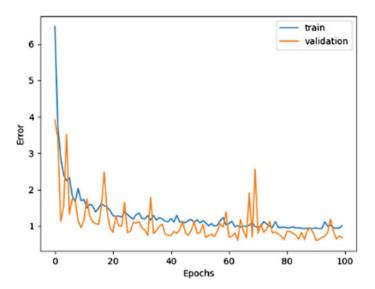

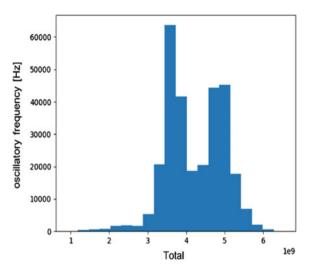

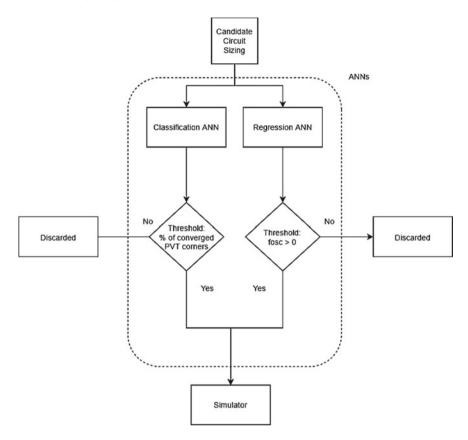

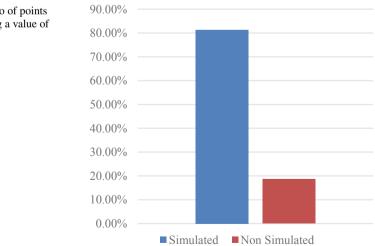

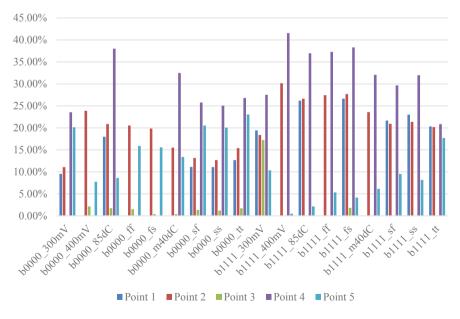

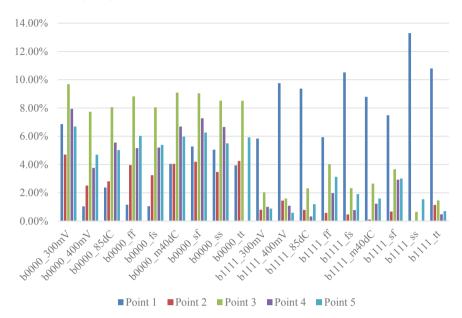

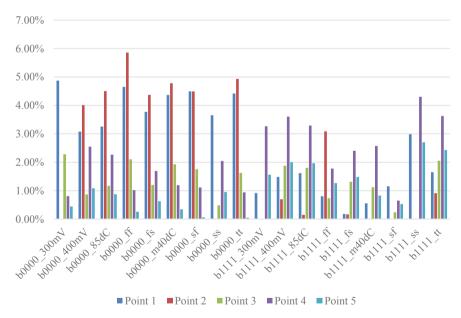

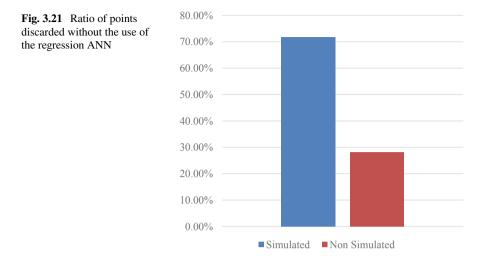

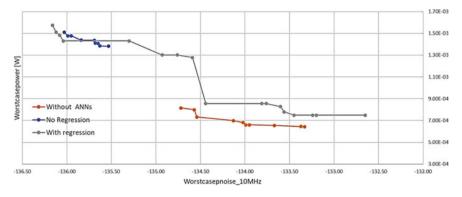

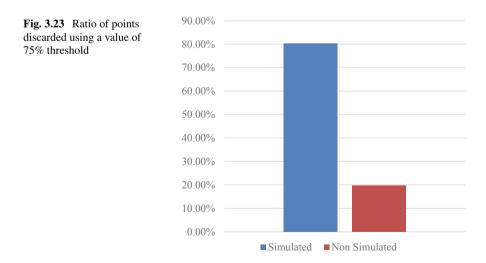

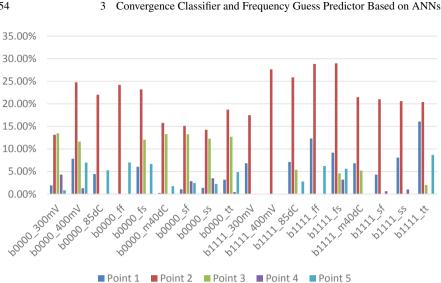

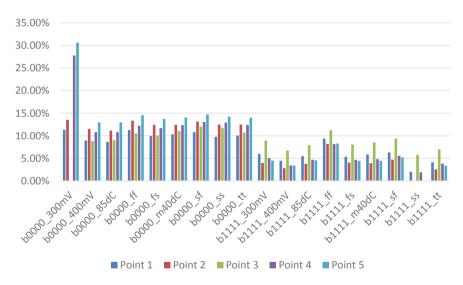

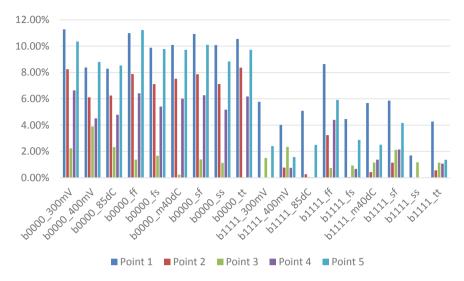

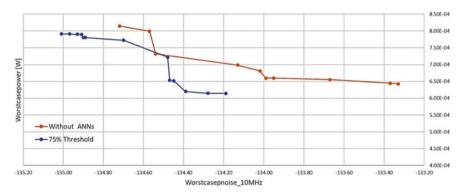

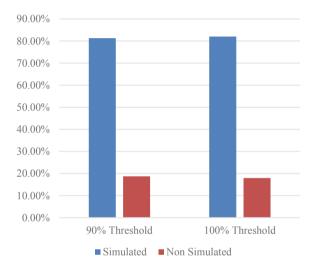

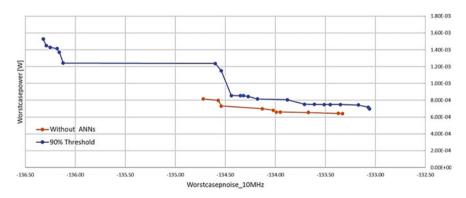

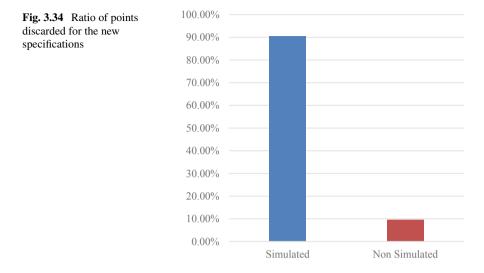

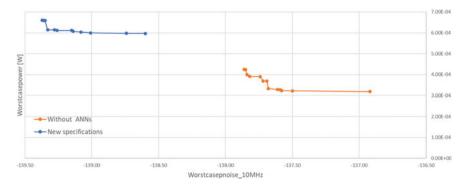

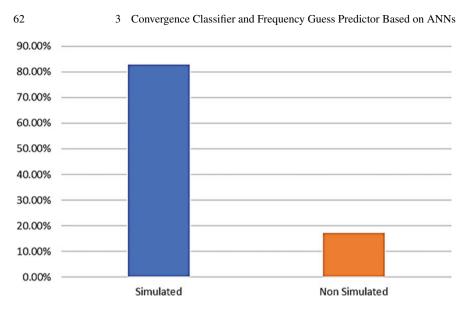

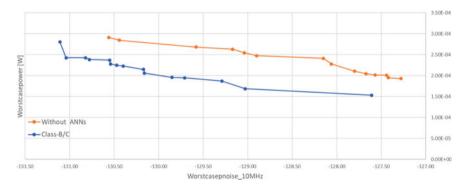

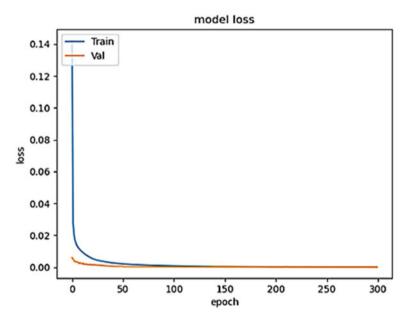

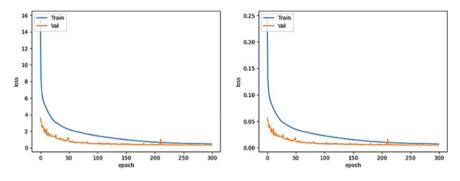

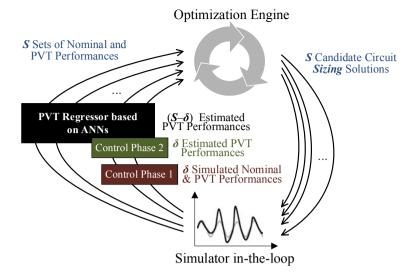

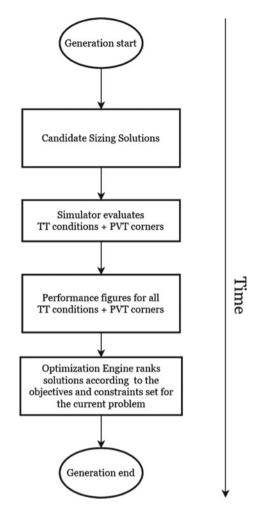

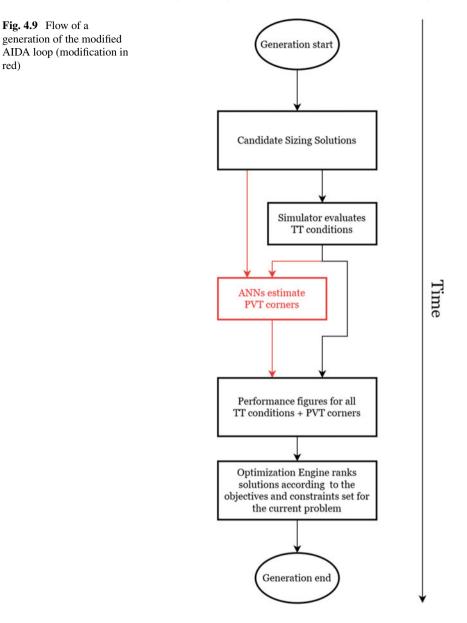

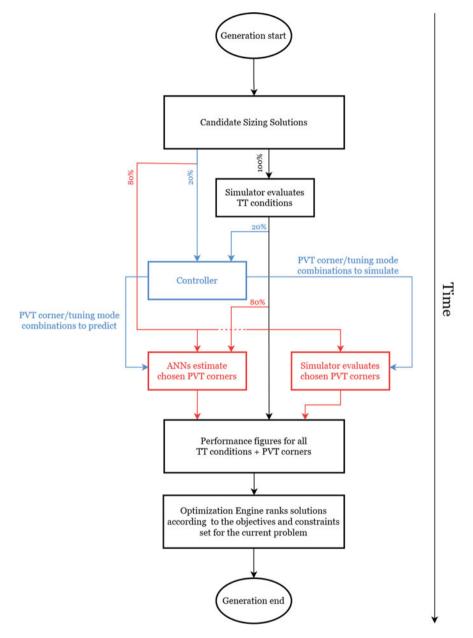

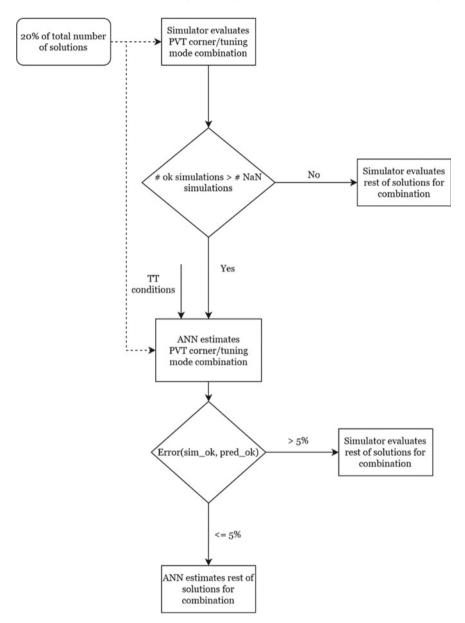

- Martins R, Lourenço N, Rodrigues S, Guilherme J, Horta N (2012) AIDA: automated analog IC design flow from circuit level to layout. In: International conference on synthesis, modeling, analysis and simulation methods and applications to circuit design (SMACD), Seville, Sept 2012