# PERANCANGAN DAN REALISASI MODULATOR DIGITAL BPSK, QPSK DAN 16-OAM PADA FPGA

# DESIGN AND REALIZATION OF DIGITAL MODULATOR BPSK, QPSK AND 16-QAM ON FPGA

Alvian Bhakti Muhammad<sup>1</sup> Denny Darlis<sup>2</sup> Arfianto Fahmi<sup>3</sup>

<sup>1,3</sup>Prodi S1 Teknik Telekomunikasi, Fakultas Teknik Elektro, Universitas Telkom <sup>2</sup>Prodi D3 Teknik Telekomunikasi, Fakultas Ilmu Terapan, Universitas Telkom

<sup>1</sup>alvian.bhakti@gmail.com <sup>2</sup>dennydarlis@telkomuniversity.ac.id <sup>3</sup>arfianto.fahmi@telkomuniversity.ac.id

### **ABSTRAK**

Inovasi pada bidang komunikasi nirkabel berkembang sangat pesat seiring dengan perilaku masyarakat modern yang memiliki mobilitas tinggi, mebutuhkan layanan yang fleksibel, kemudahan akses, kecepatan transfer data tinggi sehingga dapat memudahkan setiap aktivitas penggunanya. Kebutuhan dari setiap pengguna pun beragam, dari sekedar layanan suara, *video*, transfer data, hingga *multimedia streaming* yang menuntut kemampuan dan kehandalan dari sistem komunikasi yang digunakan. Salah satu faktor yang mempengaruhi kualitas dan kecepatan transfer data pada komunikasi nirkabel adalah modulasi. Perkembangan teknologi modulasi memungkinkan data rate (kecepatan transfer data) menjadi semakin cepat, tahan terhadap derau (*noise*), hingga keamanan (*encryption*) agar data yang dikirim lebih aman terhadap sadapan.

Implementasi modulator digital PSK (*Phase Shift Keying Modulation*) dan QAM (*Quadrature Amplitude Modulation*) pada FPGA ini dirancang untuk mempermudah perancangan sebuah hardware dengan merepresentasikan input yang disusun dengan menggunakan bahasa pemrograman VHDL. Input tersebut akan memprogram gerbanggerbang logika yang terdapat pada FPGA menjadi sebuah rangkaian yang berfungsi sebagai sebuah modulator digital yang dapat memetakan masukan bit menjadi keluaran modulator yang sudah terpetakan sesuai dengan koordinat konstelasi.

Hasil implementasi yang diharapkan adalah tiga jenis modulator digital BPSK, QPSK, dan 16-QAM yang akan diterapkan pada FPGA Xilinx Spartan 6 XC6SLX45-CSG324C, jenis modulasi yang akan digunakan dapat dipilih dengan memasukan input pada program yang terimplementasi pada FPGA. Dalam perancangan digunakan input dari perangkat laptop dengan antarmuka UART dan jenis data untuk masukan adalah ASCII 8 bit untuk kemudian dianalisis hasil simulasi modulasi dari input tersebut untuk setiap modulator menggunakan Modelsim untuk simulasi rancangan dan Chipscope untuk simulasi rancangan sistem yang terimplementasi pada FPGA.

Kata kunci: BPSK, QPSK, 16-QAM, FPGA, VHDL, UART, ASCIL.

### **ABSTRACT**

Innovations in the field of wireless communication is growing very rapidly in line with the behavior of modern societies that have high mobility, need the services that are flexible, easy access, high speed data transfer so as to facilitate any activities of its users. The needs of every user of any variety, than just voice, video, data transfer, up to a demanding streaming multimedia capabilities and reliability of the communication system used. One of the factors that affect the quality and speed of data transfer in wireless communications is modulation. Technological developments modulation allows data rate (data transfer rate) becomes faster, more resistant to noise (noise), to security (encryption) in order to secure data sent over the lead.

Implementation of digital modulator PSK (Phase Shift Keying Modulation) and QAM (Quadrature Amplitude Modulation) on FPGA is designed to simplify the design of a hardware by representing the input which are prepared using VHDL programming language. The input will be programmed logic gates contained in the FPGA into a circuit that functions as a digital modulator which can map the input bits into a modulator output that has been mapped in accordance with the coordinates of the constellation.

Expected results of the implementation are three types of digital modulator BPSK, QPSK and 16-QAM to be implemented on FPGA Xilinx Spartan-6 XC6SLX45 CSG324C, modulation type to be used can be selected by entering input on the programs implemented in the FPGA. In the design used input from laptop devices with UART interface and data types for input is ASCII 8 bit for later analysis simulation results modulation of the input to each modulator using Modelsim for simulation design and Chipscope for simulation system design implemented in the FPGA.

**Keywords:** BPSK, QPSK, 16-QAM, FPGA, VHDL, UART, ASCII.

#### 1. Pendahuluan

Kebutuhan komunikasi masyarakat modern seperti sekarang ini sudah semakin kompleks, tidak hanya sekedar layanan suara ataupun pesan, namun juga multimedia, layanan transfer data, hingga video *streaming*. Semakin kompleksnya kebutuhan komunikasi ini, semakin dibutuhkan kehandalan dari sistem komunikasi yang digunakan. Salah satu faktor yang mempengaruhi kehandalan dari suatu sistem komunikasi adalah modulasi.

Modulasi adalah proses penumpangan sinyal informasi pada sinyal pembawa, proses ini terjadi pada modulator. Modulasi dilakukan untuk memudahkan radiasi sinyal informasi ke udara, karena proses radiasi sinyal tersebut membutuhkan antena dan dimensi antena berbanding terbalik dengan frekuensi yang digunakan. Modulator yang digunakan berbeda-beda tergantung dari jenis modulasi yang digunakan.

Pada penelitian sebelumnya telah ada yang membahas mengenai perancangan modulator digital 64-QAM pada FPGA[4]. Penelitian pada tugas akhir ini akan membahas perancangan 3 jenis modulator digital BPSK, QPSK dan 16-QAM menggunakan input konfigurasi dari bahasa pemrograman Very High Speed Integrated Circuit (VSIC) Hardware Description Language (VHDL) yang akan diimplementasikan pada satu papan FPGA yang kemudian dapat dipilih jenis modulasi yang akan digunakan dengan memasukkan input pada selector modulator. Sistem modulator diberi masukan data ASCII 8 bit untuk dimodulasi oleh sistem dan dilihat hasil modulasinya pada Software Chipscope. Digunakan FPGA karena hampir semua rangkaian dalam FPGA terintegrasi di dalam chip, sehingga redaman yang akan dihasilkan akan lebih kecil.

#### 2. Dasar Teori

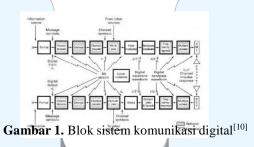

# 2.1 Sistem Komunikasi Digital [10]

Teknologi komunikasi berkembang sangat pesat dari sistem analog ke sistem digital. Sistem komunikasi analog sinyal informasi hanya ditumpangkan ke sinyal pembawa kemudian dinaikkan frekuensinya dan ditransmisikan di udara, pada sistem komunikasi digital sinyal informasi diubah dahulu menjadi bentuk bit-bit sebelum ditumpangkan ke sinyal pembawa kemudian dinaikkan frekuensinya dan ditransmisikan.

### 2.2 Modulasi [10]

Pengertian modulasi secara umum adalah penumpangan sinyal informasi kepada sinyal pembawa. Jenis modulasi yang digunakan bergantung kepada sistem komunikasi yang digunakan, modulasi analog digunakan pada sistem komunikasi digital.

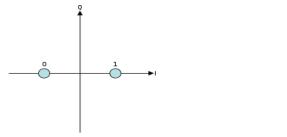

#### 2.2.1 Modulasi BPSK

Pada modulasi BPSK fasa dari frekuensi pembawa diubah-ubah antara dua nilai yang menyatakan keadaan biner 1 dan 0, dalam hal ini phasa dari frekuensi pembawa yang satu dengan yang lain berbeda sebesar 180°.

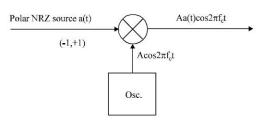

Gambar 3. Blok Modulator BPSK

## 2.2.2 Modulasi QPSK

Modulasi *Quadrature Phase Shift Keying* (QPSK) merupakan variasi dari modulasi BPSK dengan mengirimkan 2 bit data untuk satu simbolnya.

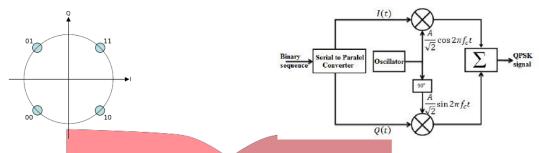

Gambar 4. Diagram konstelasi QPSK

Gambar 5. Blok modulator QPSK

# 2.2.3 Modulasi 16-QAM

Modulasi 16-QAM merupakan modulasi dengan memberikan perbedaan amplitudo dan fasa sekaligus pada simbol yang dihasilkan oleh modulator. Pada 16-QAM terdapat 2 level amplitudo dan 3 level fasa untuk satu kuadran.

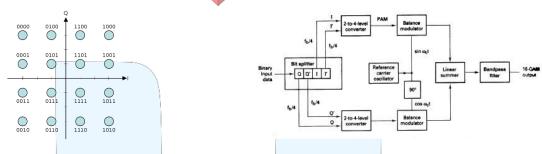

Gambar 6. Diagram Konstelasi 16-QAM

**Gambar 7.** Blok modulator 16-QAM

### 2.6 Field Programmable Gate Array

FPGA (Field Programmable Logic Array) merupakan suatu IC (Integrated Circuit) tipe HDL (High speed IC Description Language) yang dapat diprogram untuk melakukan fungsi-fungsi logika tertentu sesuai dengan kebutuhan. FPGA merupakan Programable Logic Device (PLD) yang dibangun dari sekumpulan sel fungsi logika dasar yang dapat diprogram. Sel-sel logika ini terhubung satu sama lain melalui suatu jaringan interkoneksi yang juga dapat diprogram. Penyusun dasar FPGA adalah CLB (Configurable Logic Block) dan LUT (Look Up Table).

# 3. Perancangan Sistem

Pada bagian ini akan dijelaskan alur perancangan sistem yang akan dilakukan pada Tugas Akhir ini, pada mulanya akan dilakukan penentuan blok sistem dari hasil studi literatur, kemudian dilakukan integarasi antar blok sistem tersebut sehingga membentuk sistem modulator, setelah sistem terbentuk barulah dilakukan perancangan sistem ke dalam bentuk VHDL dengen menggunakan software Xilinx ISE Design Suite 14.5. Kemudian dilakukan simulasi hasil rancangan VHDL pada software Modelsim untuk memastikan bentuk sinyal keluaran modulator adalah bentuk sinyal yang sesuai seperti pada referensi [5].

### 3.1 Penentuan Blok Modulator

Penetuan blok sistem dilakukan dengan melakukan studi literatur dari buku referensi, jurnal dan tugas akhir sebelumnya yang berkaitan dengan penilitian ini. Dari hasil studi literatur ditentukan blok-blok sebagai berikut.

a. Blok UART

Blok UART mempunyai fungsi sebagai interface antara sistem yang nantinya diimplementasikan pada FPGA dan perangkat laptop untuk memasukkan input secara *realtime* terhadap sistem. Diperlukan sinkronisasi *clock* yang sama dengan sistem agar input data ASCII 8-bit yang dimasukkan ke sistem tidak salah. b. Blok Buffer

Blok buffer berfungsi untuk menahan input dari Blok UART agar data yang dimasukkan ke sistem adalah karakter terakhir yang dimasukkan ke blok UART, jika diberikan input baru maka data yang akan dimasukkan ke dalam sistem adalah data terakhir yang dimasukkan

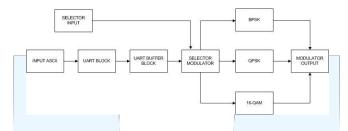

### c. Blok Selector

Blok Selector ini nantinya akan memilih jenis modulator mana yang akan digunakan dengan input tertentu yang merepresentasikan jenis modulator pada sistem. Masukan sistem akan diteruskan oleh blok selector ke modulator yang dipilih untuk digunakan.

### d. Blok Modulator

Blok modulator adalah blok yang terdiri sub-blok mapper, sub-blok mixer, sub-blok generator sinus dan sub-blok generator cosinus. Sub-blok mapper berfungsi memberikan nilai tertentu pada masukan yang merepresentasikan nilai koordinat simbol.

Untuk membentuk sinyal sinusoidal pada keluaran modulator maka keluaran sub-blok mapper dikalikan dengan sinyal sinus dan cosinus masing-masing untuk keluaran *Inphase* dan *Quadrature* mapper, Sinyal sinus dan cosinus ini dibentuk oleh generator sinus dan cosinus.

#### e. Blok Keluaran Modulator

Blok keluaran modulator berfungsi menampilkan keluaran *Inphase* dan keluaran *Quadrature* dari masing masing modulator, namun hanya keluaran modulator yang digunakan saja yang ditampilkan oleh blok keluaran modulator.

Masing-masing dari blok diatas diintegrasikan sehingga membentuk sistem modulator dengan diagaram blok seperti gambar dibawah.

Gambar 8. Diagram blok rancangan sistem

## 3.2 Perancangan Blok Sistem pada VHDL

Pada bagian awal ini akan dirancang sistem modulator dalam bahasa VHDL dengan menggunakan *software* Xilinx ISE Design Suite 14.5. Perancangan dilakukan dengan membuat setiap blok yang telah ditentukan pada subbab sebelumnya kemudian semua blok yang telah dibuat dalam bentuk VHDL tersebut diintegrasikan sehingga membentuk sistem modulator.

## 3.3 Simulasi Rancangan sistem VHDL pada Modelsim

Simulasi dilakukan untuk melihat keluaran dari sistem yang telah terancang pada VHDL apakah sesuai dengan referensi [5].

## 3.3.1 Simulasi Blok Modulator pada Sistem Modulator

Simulasi blok modulator dilakukan untuk memastikan mapper dan bentuk sinyal yang dihasilkan oleh modulator adalah hasil mapping dan bentuk sinyal hasil modulasi yang sesuai dengan referensi [5]. Simulasi dilakukan pada *software* Modelsim Altera yang dapat menampilkan bentuk sinyal *discrete time*.

Gambar 9. Simulasi mapper BPSK

Gambar 10. Simulasi modulator BPSK

Terlihat pada gambar simulasi mapper jika input modulator BPSK adalah "0" maka koordinat yang diberikan mapper terhadap input tersebut adalah (0) pada real/quadrature dan (-1) pada imag/inphase, ketika input adalah "1" maka koordinat yang diberikan mapper terhadap input tersebut adalah (0) pada real/quadrature dan (+1) pada imag/inphase. Dari hasil simulasi terlihat bahwa mapper telah sesuai dengan referensi [5]. Kemudian dapat dilhat hasil sinyal hasil mapping yang dikalikan sinyal dari generator sinus menghasilkan sinyal BPSK yang sesuai dengan referensi [5] dengan besar periode setiap satu gelombang penuh sebesar 10,015 *nanosecond*.

Gambar 11. Simulasi mapper QPSK

Gambar 12. Simulasi modulator QPSK

Terlihat pada gambar simulasi mapper jika input modulator QPSK adalah "00" maka diberikan nilai koordinat real (+1) dan koordinat imag (-1), jika input "01" maka diberikan nilai koordinat real (+1) dan koordinat imag (+1), dan jika input "11" maka diberikan nilai koordinat real (-1) dan koordinat imag (+1), sesuai dengan referensi [5]. Pada gambar simulasi modulator terlihat bentuk sinyal keluaran modulator QPSK mempunyai bentuk yang sesuai dengan sinyal QPSK pada referensi [5] dan satu gelombang penuh sinyal QPSK mempunyai periode

Gambar 13. Simulasi mapper 16-QAM

Gambar 14. Simulasi modulator 16-QAM

Terlihat pada gambar simulasi mapper 16-QAM mempunyai 4 nilai yang diberikan untuk masing-masing inputnya, contoh pada input "0000" diberikan nilai koordinat real (-1) dan koordinat imag (-1), pada input "0001" diberikan nilai koordinat real (-1) dan koordinat imag (-3), dapat dilihat bahwa mapper telah sesuai dengan referensi [5]. Pada gambar simulasi modulator dapat dilihat bahwa bentuk sinyal 16-QAM mempunyai 4 level amplitudo yang berbeda dan terdapat perbedaan fasa di setiap pergantian input yang berbeda, bentuk sinyal keluaran modulator 16-QAM telah sesuai dengan bentuk sinyal 16-QAM pada referensi [5]. Panjang periode satu gelombang penuh sinyal 16-QAM yang dihasilkan adalah 10,015 nanosecond sama seperti pada modulator BPSK dan QPSK.

# 4. Simulasi Implementasi Sistem Modulator

# 4.1 Simulasi Sistem Terimplementasi pada FPGA

Simulasi dilakukan setelah men-download-kan program yang telah dirancang dengan memberikan input dari aplikasi HyperTerminal dan memilih jenis modulator dengan mengubah switch port yang sudah dikonfigurasi sebelumnya sehingga switch port tersebut berfungsi sebagai selector modulator. Digunakan beberapa sampel masukan yang dimasukkan yaitu karakter "a" atau dengan kode ASCH 8-bit [01100001], karakter "m" [01101101] dan karakter "v" [01110110].

Gambar 15. Keluaran inphase modulator BPSK dengan data input ASCII "a"

Terlihat pada hasil keluaran modulator BPSK setiap satu simbol yang diwakili satu bit data dan membentuk satu gelombang sinusoidal mempunyai periode mendekati periode untuk satu simbol pada hasil simulasi di Modelsim yaitu sebesar 10,015 *nanosecond*. Bentuk sinyal keluaran modulator pada sistem yang terimplementasi mempunyai bentuk yang sesuai dengan bentuk sinyal BPSK pada simulasi Modelsim dan sesuai dengan bentuk sinyal BPSK [5].

Gambar 16. Keluaran inphase Modulator QPSK QPSK dengan input ASCII "a"

**Gambar 17.** Keluaran quadrature Modulator dengan data input ASCII "a"

Pada modulator QPSK panjang satu simbol yang terdiri dari dua bit data dan diwakili satu gelombang mempunyai periode yang mendekati dari periode satu simbol pada hasil simulasi pada Modelsim. Bentuk sinyal keluaran pada sistem yang terimplementasi pada FPGA sesuai dengan bentuk sinyal hasil simulasi pada modelsim dan bentuk sinyal pada referensi [5]

Gambar 18. Keluaran inphase modulator 16-QAM

Gambar 19. Keluaran quadrature modulator 16-QAM

dengan data input ASCII "a"

dengan input ASCII "a"

Pada keluaran modulator 16-QAM memliki panjang simbol yang terdiri dari 4 bit data sekitar 10 *nanosecond* sama seperti pada modulator BPSK dan QPSK. Bentuk sinyal keluaran pada sistem yang terimplementasi pada FPGA sesuai dengan bentuk sinyal hasil simulasi pada modelsim dan bentuk sinyal pada referensi [5]

Dari parameter yang didapat pada simulasi, dapat diukur *symbol rate*, bit rate, dan propagation delay yang dibutuhkan untuk menghasilkan satu simbol sinyal dari setiap modulator.

Tabel 1. Parameter yang didapat dari simulasi sistem modulator

| Parameter                                              | Nilai      |

|--------------------------------------------------------|------------|

| Clock                                                  | 10 ns      |

| Perioda                                                |            |

| -Perioda sinyal pembawa (sinus & cosinus)              | 100 clock  |

| -Perioda <i>mapper</i> BPSK                            | 10,015 ns  |

| -Perioda mapper QPSK                                   | 10,015 ns  |

| -Perioda <i>mapper</i> 16-QAM                          | 10,015 ns  |

| Panjang keluaran mapper Quadrature                     | 16 bit     |

| Panjang keluaran mapper Inphase                        | 16 bit     |

| Panjang keluaran sistem modulator (Inphase+Quadrature) | 17 bit     |

| Bit rate BPSK                                          | 99,85 Mbps |

| Bit rate QPSK                                          | 199,7 Mbps |

| Bit rate 16-QAM                                        | 399,4 Mbps |

Modulator mengubah sinyal *baseband* menjadi sinyal *passband* dengan cara mengalikan keluaran sinyal *baseband* dengan sinyal pembawa. Hasil keluaran modulator BPSK terdiri dari satu bit setiap satu simbol, pada QPSK dua bit untuk satu simbol dan pada 16-QAM empat bit untuk setiap simbol.

Dari simulasi yang telah dilakukan, didapat beberapa parameter yaitu *symbol rate*, *bit rate*, dan *delay* propagasi. Parameter tersebut didapat dari persamaan berikut [10]

Dari persamaan tersebu didapat symbol rate, bit rate, dan delay propagasi pada modulator BPSK sebagai berikut

$$\frac{1}{100,15} = 99,85$$

Didapat parameter yang sama untuk modulator QPSK adalah sebagai berikut

$$\frac{1}{100,15} = 99,85 = \frac{1}{100,15} = 99,85 = \frac{1}{100,15} = \frac{1$$

Dan parameter pada modulator 16-QAM adalah sebagai berikut.

$$\frac{1}{100,15} = 99,85$$

$$\frac{1}{100,15} = 99,85$$

$$\frac{1}{100,15} = \frac{1}{100,15} = \frac$$

Dari hasil penelitian yang dilakukan, dapat disimpulkan bahwa :

- a. Sistem modulator digital BPSK, QPSK dan 16-QAM beserta modulator selector untuk dapat diimplementasikan pada FPGA. Hasil implementasi menghasilkan 16 bit sinyal *Quadrature* dan 16 bit sinyal *Inphase*.

- b. Penambahan input sistem modulator dengan bentuk data ASCII 8-bit melalui port UART pada FPGA, namun perlu dibuat modul interface antara perangkat laptop dan UART tersebut dan dilakukan sinkronisasi agar masukan tersebut adalah data yang tepat.

- c. Berdasarkan hasil simulasi sistem dan analisis hasil implementasi didapat bit rate pada modulator BPSK sebesar 99,85 Mbps, pada modulator QPSK sebesar 199,70 Mbps dan pada modulator 16-QAM sebesar 399,40 Mbps dengan *symbol rate* untuk setiap simbol pada masing-masing modulator adalah 99,85 *symbol per second*. Dan *delay* propagasi untuk setiap *bit* adalah 10,015 *nanosecond* pada modulator BPSK, 4,933 *nanosecond* pada modulator QPSK dan 2,503 *nanosecond* pada modulator 16-QAM.

- d. Berdasarkan hasil sintesis blok sistem modulator BPSK, QPSK dan 16-QAM didapatkan jumlah resource yang dibutuhkan adalah jumlah slice 199 dari 54576 yang tersedia atau 0% dari resource Spartan-6 XC6SLX45-CSG324C, jumlah slice LUT's 398 dari 27288 yang tersedia atau 1% dari resource, jumlah LUT-FF pairs 177 dari 420 yang tersedia atau 42% dari resource, jumlah IOB 40 dari 218 yang tersedia atau 18% dari resource, jumlah BUFG/BUFGCTRL/BUFHCEs 4 dari 16 yang tersedia atau 25% dari resource dan jumlah DSP48A1s 5 dari 58 yang tersedia atau 8% dari resource. Dari hasil sintesis tersebut dapat disimpulkan bahwa hasil implementasi sistem tidak melebihi source pada FPGA sehingga dapat diimplementasikan.

### **DAFTAR PUSTAKA**

- [1] Chu, Pong P. 2008. FPGA Prototyping by VHDL Examples. Cleaveland State University: John Wiley & Sons, Inc.

- [2] Darlis, Denny. 2010. Perancangan dan Implementasi Prosesor Berbasis OFDM untuk Prototipe Modem PLC pada FPGA. Institut Teknologi Telkom: tidak diterbitkan.

- [3] Dwi Utami, Rizki. 2013. Perancangan dan Realisasi Demapper 16-QAM pada Sistem DVB-C menggunakan FPGA. Institut Teknologi Telkom: Tidak diterbitkan.

- [4] Falaq, Fahrizal. 2013. Desain dan Implementasi Modulator Digital 64-QAM. Institut Teknologi Telkom: Tidak diterbitkan.

- [5] Haykin, Simon. 2000. Communication Systems. Ontario: John Wiley & Sons, Inc.

- [6] Khairuddin, A. Labib. 2011. Perancangan dan Implementasi Prosesor FFT 256 Titik-Ofdm Baseband Berbasis Pengkodean VHDL pada FPGA. Institut Teknologi Telkom: Tidak diterbitkan.

- [7] Merliyasari, Prima. 2013. *Perancangan dan Implementasi Modulator 16-QAM untuk DVB-C pada FPGA*. Institut Teknologi Telkom: Tidak diterbitkan.

- [8] Popescu, S.O., Gontean, A.S, Ianchis, D. 2011. QPSK Modulator on FPGA. IEEE: Romania.

- [9] Popescu, S.O., G. Budura and A.S Gontenan. 2010. Review of PSK and QAM Digital modulation techniques on FPGA. IEEE: Romania.

- [10] Proakis, John G., Massoud Salehi. 2008. Digital Communications. Boston: McGraw-Hill.

- [11] Sklar, Bernard. 2001. Digital Communications: Fundamentals and Applications. New Jersey Pretince Hall.

- [12] Vandenbout, Dave. 2014. FPGAs?! Now What?. XESS Corporation.